# Demystifying Switching Power Supplies Raymond A. Mack, Jr.

Demystifying Technology Series m

Books By Engineers, For Engineers

# Demystifying Switching Power Supplies

# Demystifying Switching Power Supplies

Raymond A. Mack, Jr.

AMSTERDAM • BOSTON • HEIDELBERG • LONDON NEW YORK • OXFORD • PARIS • SAN DIEGO SAN FRANCISCO • SINGAPORE • SYDNEY • TOKYO Newnes is an imprint of Elsevier

Newnes is an imprint of Elsevier 30 Corporate Drive, Suite 400, Burlington, MA 01803, USA Linacre House, Jordan Hill, Oxford OX2 8DP, UK

Copyright © 2005, Elsevier Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

Permissions may be sought directly from Elsevier's Science & Technology Rights

Department in Oxford, UK: phone: (+44) 1865 843830, fax: (+44) 1865 853333, e-mail: permissions@elsevier.com.uk. You may also complete your request on-line via the Elsevier homepage (http://elsevier.com), by selecting "Customer Support" and then "Obtaining Permissions."

Recognizing the importance of preserving what has been written, Elsevier prints its books on acid-free paper whenever possible.

### Library of Congress Cataloging-in-Publication Data

Mack, Raymond.

Demystifying switching power supplies / Raymond Mack.

p. cm.

Includes bibliographical references and index.

ISBN 0-7506-7445-8 (alk. paper)

1. Switching circuits—Design and construction. 2. Power semiconductors—Design and construction. 3. Semiconductor switches—Design and construction. 4. Switching power supplies—Design and construction. I. Titile.

TK7868.S9M24 2005 621.31'7—dc22

2004029371

### **British Library Cataloguing-in-Publication Data**

A catalogue record for this book is available from the British Library.

For information on all Newnes publications visit our Web site at www.books.elsevier.com

05 06 07 08 09 10 10 9 8 7 6 5 4 3 2 1

Printed in the United States of America

# Working together to grow libraries in developing countries

www.elsevier.com | www.bookaid.org | www.sabre.org

**ELSEVIER**

BOOK AID

Sabre Foundation

# **Contents**

| Preface                                      | ix |

|----------------------------------------------|----|

| Introduction                                 | xi |

| Chapter One: Basic Switching Circuits        | 1  |

| Energy Storage Basics                        |    |

| Buck Converter                               | 4  |

| Boost Converter                              | 6  |

| Inverting Boost Converter                    | 9  |

| Buck-Boost Converter                         | 10 |

| Transformer Isolated Converters              | 11 |

| Synchronous Rectification                    | 16 |

| Charge Pumps                                 | 17 |

| Chapter Two: Control Circuits                | 21 |

| Basic Control Circuits                       |    |

| The Error Amplifier                          | 26 |

| Error Amplifier Compensation                 | 28 |

| A Representative Voltage Mode PWM Controller | 33 |

| Current Mode Control                         | 39 |

| A Representative Current Mode PWM Controller | 41 |

| Charge Pump Circuits                         | 45 |

| Multiple Phase PWM Controllers               | 49 |

| Resonant Mode Controllers                    | 50 |

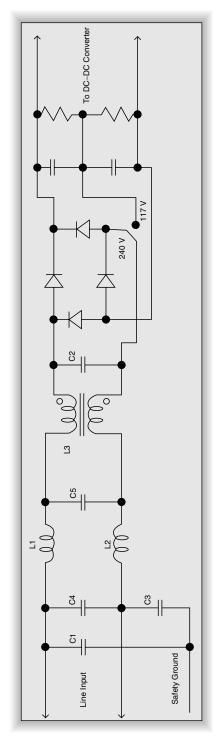

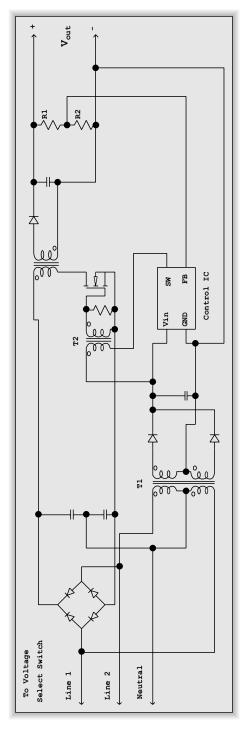

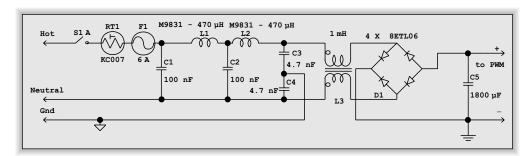

| Chapter Three: The Input Power Supply        | 51 |

| Off-Line Operation                           |    |

| Radio Interference Suppression               |    |

| Safety Agency Issues                         |    |

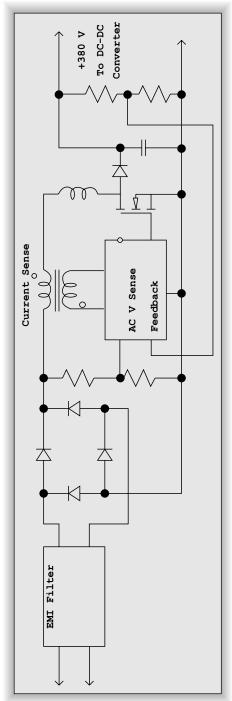

| Power Factor Correction                      |    |

| In-Rush Current                              | 64 |

## **Contents**

|     | Hold-Up Time                              | 66  |

|-----|-------------------------------------------|-----|

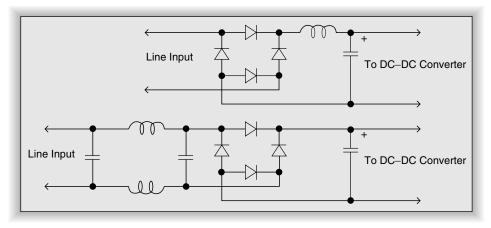

|     | Input Rectifier Considerations            | 69  |

|     | Input Reservoir Capacitor Characteristics | 70  |

| Cha | pter Four: Non-Isolated Circuits          | 73  |

|     | General Design Method                     | 75  |

|     | Buck Converter Designs                    | 76  |

|     | Boost Converter Designs                   | 86  |

|     | Inverting Designs                         | 94  |

|     | Step Up/Step Down (Buck/Boost) Designs    | 97  |

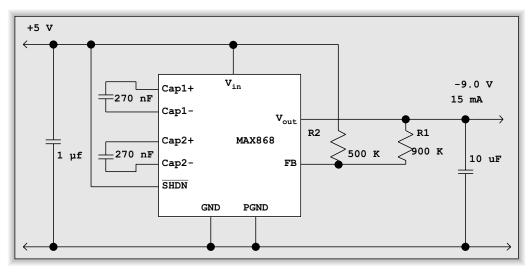

|     | Charge Pump Designs                       | 102 |

|     | Layout Considerations                     | 107 |

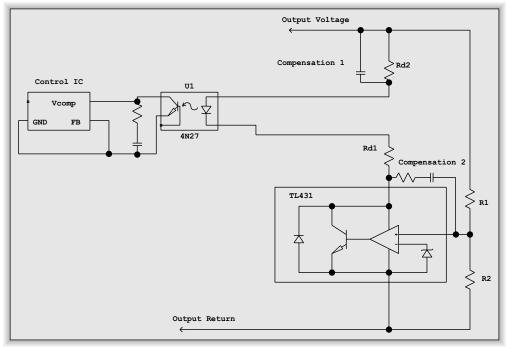

| Cha | pter Five: Transformer-Isolated Circuits  | 111 |

|     | Feedback Mechanisms                       | 113 |

|     | Flyback Circuits                          | 121 |

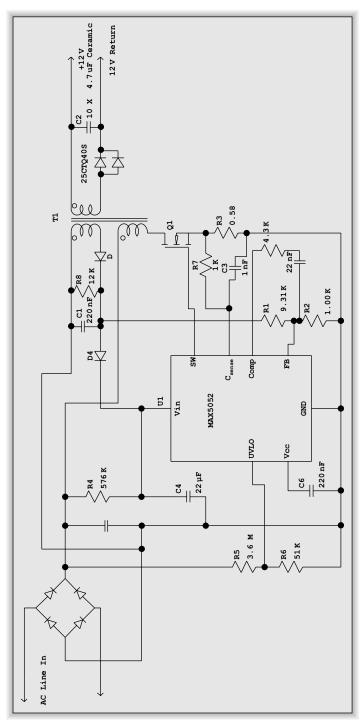

|     | Practical Flyback Circuit Design          | 129 |

|     | Off-Line Flyback Example                  | 129 |

|     | Non-Isolated Flyback Example              | 137 |

|     | Forward Converter Circuits                | 141 |

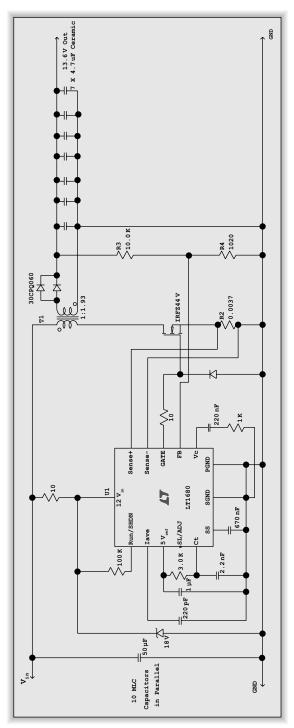

|     | Practical Forward Converter Design        | 143 |

|     | Off-Line Forward Converter Example        | 144 |

|     | Non-Isolated Forward Converter Example    |     |

|     | Push-Pull Circuits                        | 152 |

|     | Practical Push-Pull Circuit Design        |     |

|     | Half Bridge Circuits                      |     |

|     | Practical Half Bridge Circuit Design      | 161 |

|     | Full Bridge Circuits                      | 164 |

| Cha | pter Six: Passive Component Selection     | 167 |

|     | Capacitor Characteristics                 | 169 |

|     | Aluminum Electrolytic Capacitors          | 171 |

|     | Solid Tantalum and Niobium Capacitors     | 173 |

|     | Solid Polymer Electrolytic Capacitors     | 175 |

|     | Multilayer Ceramic Capacitors             | 176 |

|     | Film Capacitors                           | 180 |

| Resistor Characteristics                                | 181 |

|---------------------------------------------------------|-----|

| Carbon Composition Resistors                            | 183 |

| Film Resistors                                          | 183 |

| Wire Resistors                                          | 184 |

| Chapter Seven: Semiconductor Selection                  | 187 |

| Diode Characteristics                                   |     |

| Junction Diodes                                         | 189 |

| Schottky Diodes                                         | 194 |

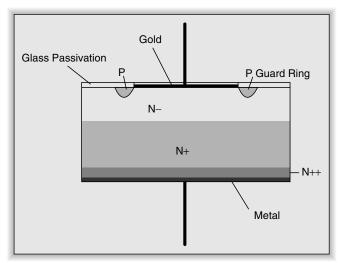

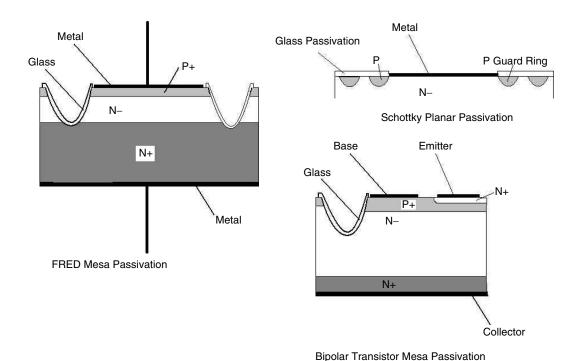

| Passivation                                             | 197 |

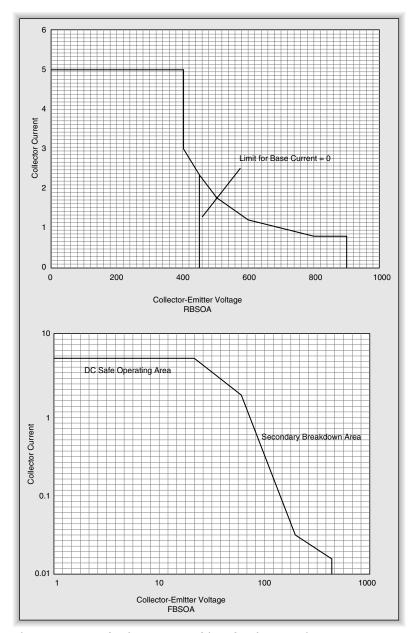

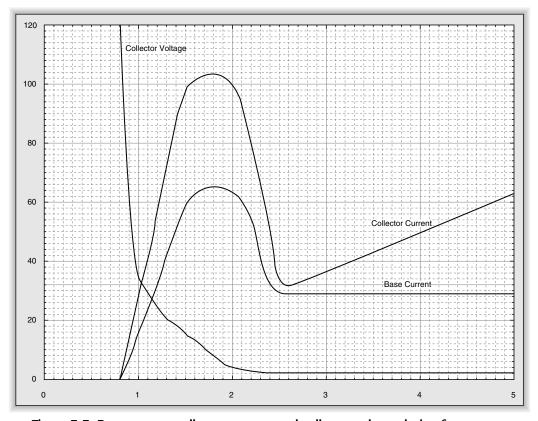

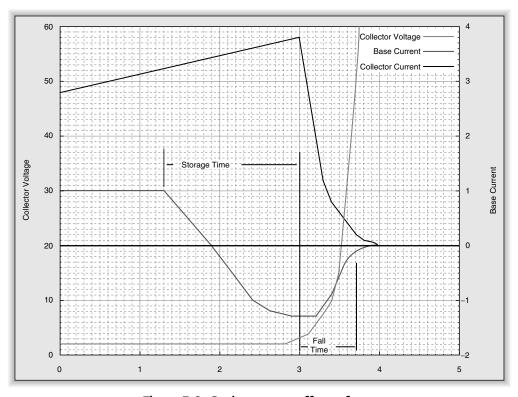

| Bipolar Transistors                                     | 197 |

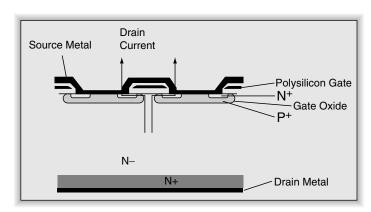

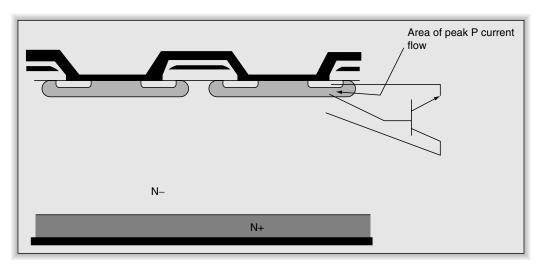

| Power MOSFETs                                           | 204 |

| Gate Drive                                              | 208 |

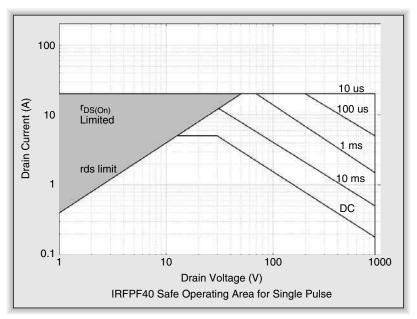

| Safe Operating Area and Avalanche Rating                | 219 |

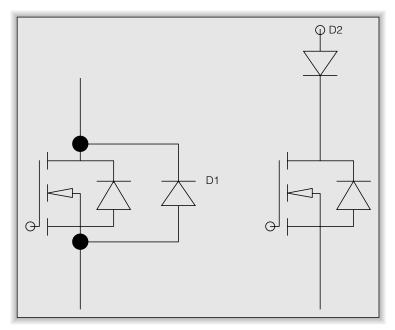

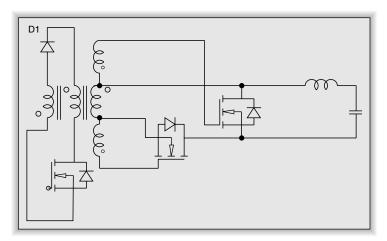

| Synchronous Rectification                               | 222 |

| Sense FETs                                              | 229 |

| Package Options                                         | 229 |

| IGBT Devices                                            | 230 |

| Chapter Eight: Inductor Selection                       | 235 |

| Properties of Real Inductors                            |     |

| Core Properties                                         | 240 |

| Designing a Powder Toroid Choke Core                    | 250 |

| Choosing a Boost Converter Core                         | 256 |

| Chapter Nine: Transformer Selection                     | 261 |

| Transformer Properties                                  |     |

| Safety Concerns                                         | 266 |

| Practical Construction Considerations                   | 267 |

| Choosing a Forward Converter Transformer Core           | 271 |

| Practical Flyback Core Considerations                   | 272 |

| Choosing a Flyback Converter "Transformer" Core         | 273 |

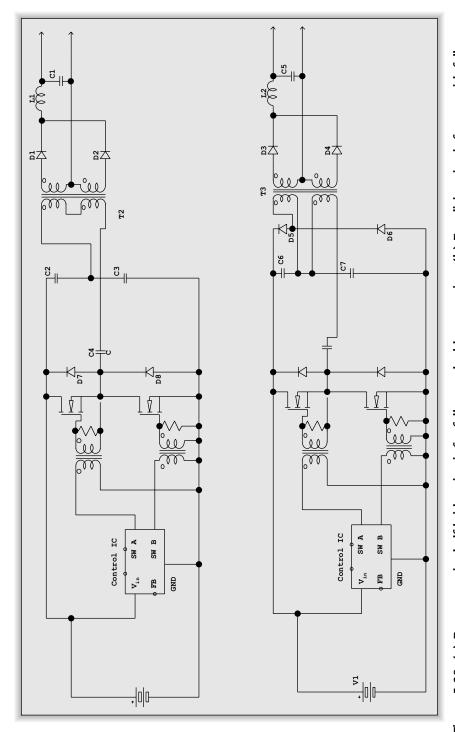

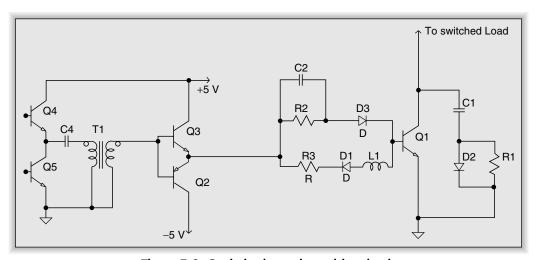

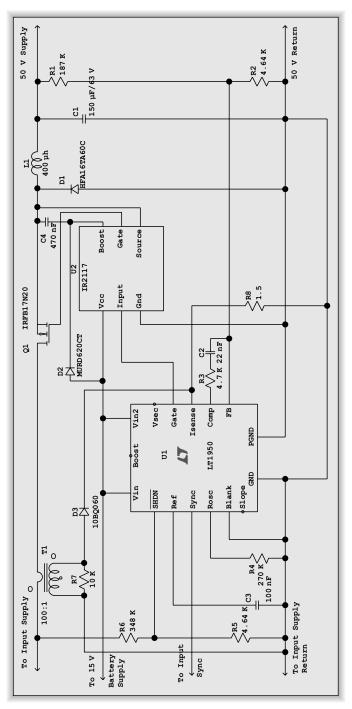

| Chapter Ten: A "True Sine Wave" Inverter Design Example | 277 |

| Design Requirements                                     |     |

| Design Description                                      |     |

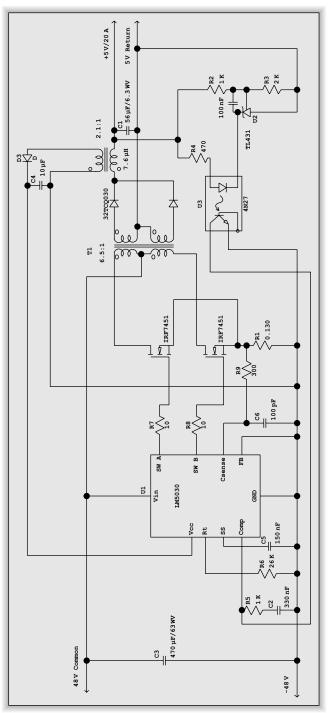

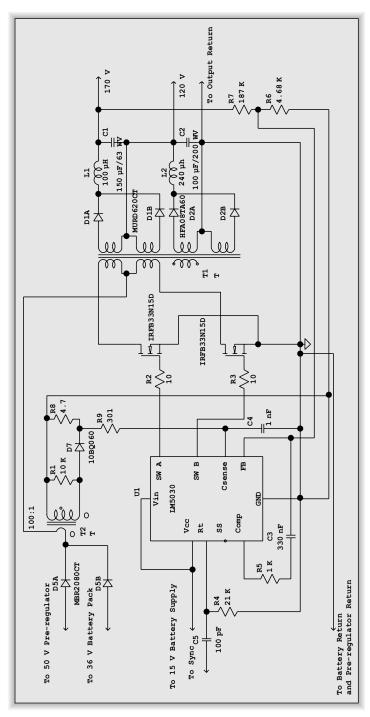

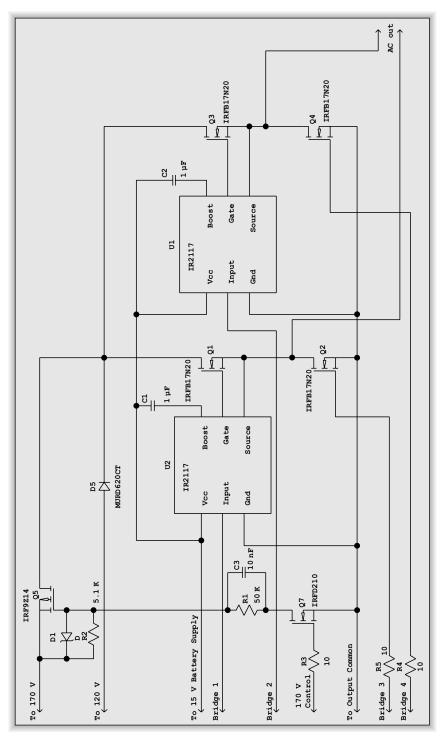

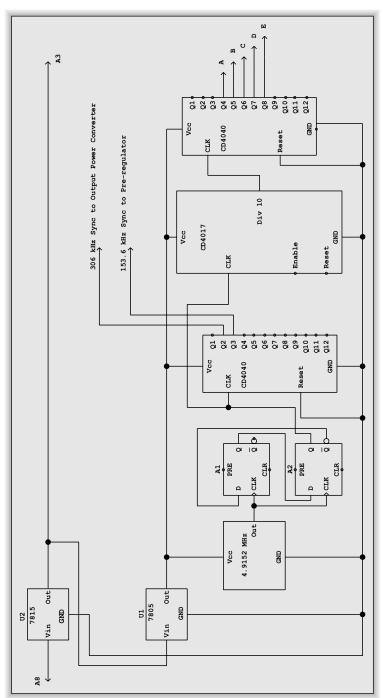

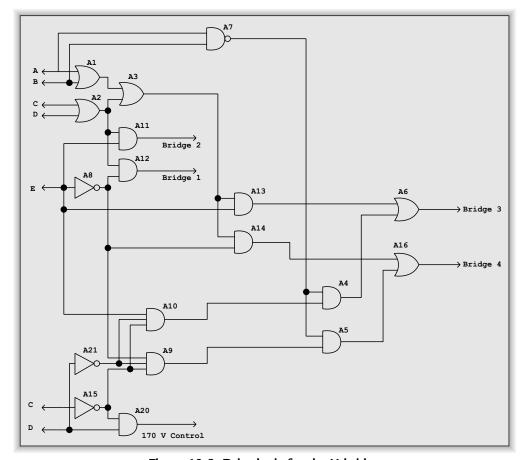

| Preregulator Detailed Design                            | 286 |

# Contents

| Output Converter Detailed Design     | 290 |

|--------------------------------------|-----|

| H Bridge Detailed Design             |     |

| Bridge Drive Detailed Design         |     |

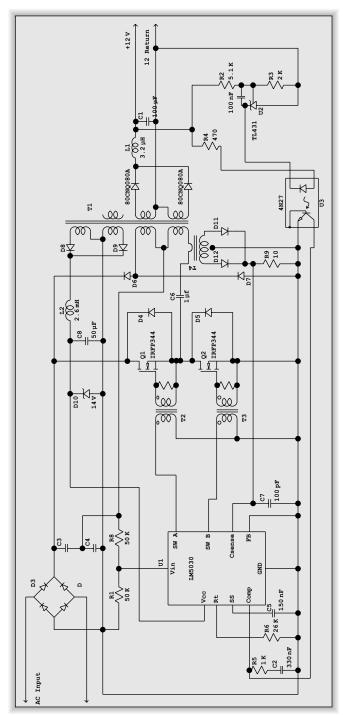

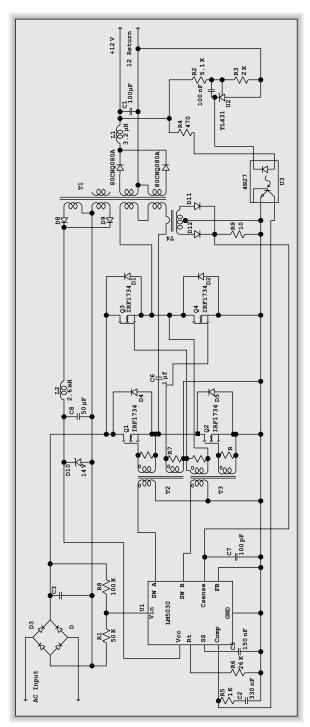

| Chapter Eleven: A PC Off-Line Supply | 299 |

| Setting Requirements                 |     |

| The Input Supply                     |     |

| DC-DC Converter                      |     |

| Diode Selection                      |     |

| Inductor Designs                     | 310 |

| Capacitor Designs                    |     |

| Transformer Design                   |     |

| Index                                | 319 |

# Preface

This book is intended for those who need to understand how a switching power supply works. I intend to provide enough information so you can intelligently specify a custom off-line supply from a power supply manufacturer. You should also gain enough information to be able to design a DC–DC converter. I have included basic analog design information for those whose primary electronics background is not analog circuits. Then I build on that basic information to show how to design and analyze practical switching power supplies. Those with a strong background in analog circuitry may want to skim over the preliminary data.

In numerous places I skip over the details of derivations and transformations of equations. The details of those transformations are left as an exercise for the reader.

There are two broad classes of power supplies: linear and switching. Linear supplies use time continuous control of the output. Switching supplies are time-sampled systems that use rectangular samples to control the output. This book explores each of the variations of switching power supplies.

# Acknowledgments

Like most work, this book is built on the efforts of many others. I wish to acknowledge the large contribution to my understanding of switching power supplies by the authors of the Motorola application book *Linear/Switchmode Voltage Regulator Handbook*, the International Rectifier *HDB-3 Power MOSFET HEXFET Databook*, and the Philips *Switch Mode Power Supply* Semiconductor application book (an excellent book but available only on their website).

I also wish to acknowledge the gracious contributions by Linear Technology Corporation. Linear Technology gives away their program SwitcherCAD III. It is intended for use by their customers, but it is free to all who want to use it. Most of the schematics in this book were initially prepared using the drafting functions of SwitcherCAD III.

# Introduction

The principles of switching power supplies have been used for over 100 years (though people didn't know that's what they were). The ignition system used in a gasoline engine was the earliest version of a flyback switching power supply. The next general use of switching supplies was in the high voltage section of televisions. Again, this is an example of a rudimentary flyback supply. The flyback name comes from the short time period where the spot on the television CRT is moved from the right side of the screen back to the left side of the screen (it would "fly back"). The rapid change in current in the deflection coil causes a very large voltage to be generated. This was used to advantage in televisions to create the large acceleration potential necessary for the CRT.

Widespread switching supply use was limited to television high voltage service until the late 1960s because of limited capabilities of the three major components in a switching supply: the magnetics, the switch, and the rectifier. Components were available for switching supply use in the early 1960s with the advent of high voltage bipolar transistors, but they weren't economically feasible for low wattage uses until the price of semiconductors became reasonable. Since 1970, advances in all component categories have changed the power supply market to the point where linear power supplies are almost nonexistent above the level provided by three terminal linear regulators. Advances in semiconductors allow single package switching power supplies with multi-watt capability. These designs use the IC, an inductor, and a couple of capacitors to produce a complete voltage regulator in a volume smaller than a single TO-3 switching transistor from the 1960s.

The price per watt of AC line operated power supplies has dropped to the point that it is not cost effective to design and build such a supply in-house unless extremely large quantities are involved. Many companies market lines of standard output voltage supplies. Most of these companies can also supply nonstandard voltages based on standard designs for nominal design fees.

Most of the major linear IC manufacturers (Linear Technology, Maxim, TI, National Semiconductor, Analog Devices, etc.) provide a line of switching regulator circuits suitable for local voltage regulation or voltage conversion. Modern devices from these manufacturers are extremely small and efficient. This is true especially of devices intended for battery-operated equipment where maximum operation between charging is important. Modern devices frequently integrate the control circuit, the switch, and the required rectifiers in the same package.

The passive component manufacturers have been busy improving components as well. The magnetic materials companies (Ferroxcube, Siemens, Micrometals, Magnetics division of Spang & Co., etc.) have extended the useful range of transformers and chokes from the low kHz range (10–50 kHz) in the 60s to well above 1 MHz today. This improvement has allowed much smaller filter capacitors and magnetic cores in modern designs. Capacitor manufacturers have also improved filter capacitors for use in switchers. Ordinary electrolytic capacitors have a very large equivalent series resistance that causes them to dissipate power when a rapidly varying DC voltage is applied. If this equivalent AC current is too high, these electrolytics will heat to the point of explosion. All electrolytic capacitor manufacturers now make lines of capacitors that are designed to limit this equivalent series resistance.

# Comparison of Linear and Switching Supplies

A comparison of representative linear and switching power supplies shows why we would want to use a switching supply in most applications.

A linear power supply can only produce a voltage lower than the input voltage. All linear regulators require the input voltage to be at least a minimum amount above the output voltage. This is called the drop-out voltage. The drop-out voltage is the parameter that drives the calculations for efficiency and worst-case power dissipation.

Let's look at the operation of a device that operates at 6.0 V and has a maximum current draw of 2 A. A representative linear regulator will have a drop-out voltage of 2 V. If we choose to use a lead acid battery, the battery will be discharged when the voltage reaches around 1.9 V per cell. Since we require a minimum of 8 V

(6 V for the load plus the 2 V drop-out voltage) for proper operation, we will require a minimum of 5 cells to provide the necessary voltage. This yields a minimum input voltage of 9.9 V when the battery is discharged. The power in the load is 12 W with 2 A supplied, and the regulator must dissipate 7.8 W when the battery is discharged. This yields an efficiency of 60%. When the battery is fully charged, the cell voltage is 2.26 V and the battery supplies 11.3 V. The load power is still 12 W. The regulator must now dissipate 10.6 W, which yields an efficiency of 53%.

The situation is better if we decide to draw less from each cell. We can increase the efficiency and decrease the cost of the battery (at the cost of more frequent recharge cycles) if we stop operation at a cell voltage of 2.0 V. Now we only require 4 cells for operation. The regulator dissipates 4 W at end of charge so the efficiency increases to 75%. At full charge the efficiency has only improved to 67%.

In the first example, 2 of the 5 cells contribute all of their energy to heat. In the second example, 1 of the 4 cells is used entirely for heat. You can see that linear regulation is a very expensive way to provide a constant voltage in a battery-operated system.

A simple switching power supply can be built for the application described above with FET switches that have an on resistance on the order of 0.008 Ohm. The commutating diode can be a Schottky diode with an on voltage of only 0.5 V. As a first approximation, the power dissipated in the switch is a maximum of 0.032 W, and the power dissipated by the diode is 1.0 W. The efficiency at full charge is 92 % and the efficiency at discharge is close to 99%. What is even better is that these relative efficiencies will hold for a 4-cell battery, a 6-cell battery, or a 12-cell battery.

There is another advantage of switching power supplies over a linear supply. With the linear supply, we were restricted to a battery of 4 cells or more for proper operation. A switching power supply can be built to provide the necessary power from 1 to 3 cells that will still have better efficiency than the linear supplies.

The situation is similar for line operated power supplies. A line operated linear supply requires a transformer. A linear supply that delivers 1000 W of power

requires a transformer weighing approximately 100 pounds (and heavier if both 50 Hz and 60 Hz operation is required), requires massive heat sinks for the semiconductors and blowers for the heat sinks, and occupies more than a cubic foot of volume. If 110 V or 220 V operation is required, a linear supply will need manual or complicated electronic switching to handle both line voltages. By contrast, a switching supply can be designed that handles 110 or 220 and 50 Hz or 60 Hz without selection circuitry, weighs less than 50 pounds, and occupies one-quarter the volume of the linear supply. The switching power supply also costs a fraction of the linear supply.

Switching supplies are not always the best solution. High frequency noise is an inherent part of the output of a switching power supply. Linear supplies can be 100 to 1000 times quieter than a switching supply. A linear supply is usually a requirement for very noise sensitive analog circuits. Where maximum efficiency is required, modern systems will frequently pre-regulate a voltage with a switching supply to a value just above the drop-out voltage and use a linear supply to provide the low noise power to the analog circuits. Another disadvantage of switching supplies is that there is typically a longer recovery time from a large step change in load current or a step change in input voltage when compared with linear supplies.

Linear supplies are usually a better solution for very low power applications. In the example above, we approximated the loss in the switch as the I<sup>2</sup>R power. A better analysis will include losses in the switch during the turn on and turn off times as well as the power needed to drive the switch. Additionally, there are special purpose linear regulators that have very low drop-out voltages for use in low power applications. Both of these factors can tip the balance toward linear regulators in some low power applications.

# CHAPTER 1

# **Basic Switching Circuits**

- Energy Storage Basics

- Buck Converter

- Boost Converter

- Inverting Boost Converter

- Buck-Boost Converter

- Transformer Isolated Converters

- Synchronous Rectification

- Charge Pumps

# **Basic Switching Circuits**

In this chapter, we will look at the time domain description of ideal inductors and capacitors and review ideal versions of each type of switching supply. In later chapters, we will look at the magnetic, electrical, and parasitic properties of inductors and capacitors and their effect on the design of individual components.

# **Energy Storage Basics**

Equation (1-1) contains the definition of inductance. An inductor has an inductance of one henry if a change of current of one ampere/second produces one volt across the inductor.

$$V = L \, di/dt \tag{1-1}$$

This is Lenz's law. The first consequence of Eq. (1-1) is that the current through an inductor cannot change instantaneously. To do so would generate an infinite voltage across the inductor. In the real world, things such as an arc across switch contacts will limit the voltage to very high, but not infinite, values. The other consequence of Eq. (1-1) is that the voltage across an inductor changes instantaneously from positive to negative when we switch from storing energy in the inductor (di/dt) is positive) to removing energy from it (di/dt) is negative). Equation (1-2) is the converse of Eq. (1-1) and is used to determine the current in the inductor when the voltage is known.

$$I = 1/L \int V dt + I_{initial}$$

(1-2)

Equation (1-3) contains the definition of a capacitor. It states that a capacitor is one farad if storing one coulomb of charge creates one volt.

$$Q = CV (1-3)$$

Equations (1-4) and (1-5) describe a capacitor in terms of voltage and current (where charge is the integral of current and current is dq/dt).

$$V = 1/C \int i \, dt + V_{\text{initial}} \tag{1-4}$$

$$I = C \frac{dv}{dt} \tag{1-5}$$

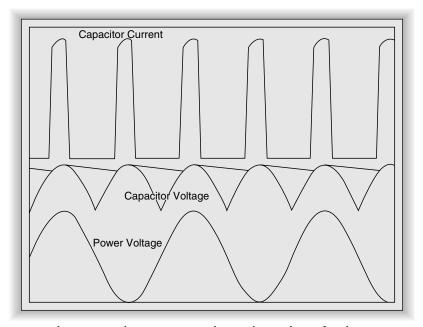

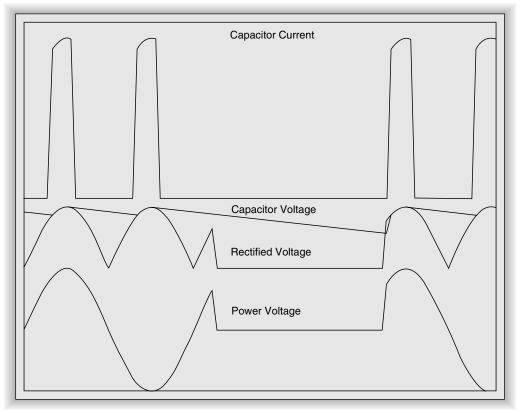

The current waveform of the filter capacitor of a switching power supply is typically a sawtooth waveform. The goal of the capacitor is to limit the change in voltage (ripple voltage). There are two variables in Eq. (1-4) that can control the change in output voltage. We can either make the capacitance large or make dt small to control the voltage ripple. One of the major advantages of switching power supplies is that we can make dt very small (a high switching frequency) which allows the value of C to also be very small.

## **Buck Converter**

Figure (1-1) shows an ideal buck converter regulator made of an ideal voltage source, an ideal voltage controlled switch, an ideal diode, an ideal inductor, an ideal capacitor, and a load resistor. It is called a buck converter because the voltage across the inductor "bucks" or opposes the supply voltage. The output voltage of a buck converter is always less than the input voltage. This ideal regulator is designed to use a 20 V source and provide 5 V to the 10 ohm load. The switch is opened and closed once every 10  $\mu$ s. The switch produces a pulse width modulated waveform to the passive components. When the regulator is at steady state, the output voltage is:

$$V_{out} = V_{in} * Duty Cycle$$

(1-6)

This equation is independent of the value of the inductor, the load current, and the output capacitor as long as the inductor current flows continuously. This equation assumes that the inductor voltage has a rectangular shape.

The diode acts as a voltage controlled switch. It provides a path for the inductor current once the switch is opened. No current flows through the diode while the inductor is charging because it is reverse biased. When the control switch opens, the inductor current flows through the diode.

Figure 1-1: Idealized buck converter regulator

We design switching supplies with the simplifying assumption that the applied voltage to the inductor during charging is a perfect rectangular wave. Our example power supply has voltage output ripple of 20 mV. The perfect rectangle is a good approximation since the change in inductor voltage during charging is 0.02/15 or 0.13% and the variation on discharge is 0.02/5 or 0.4%. The constant voltage of the rectangular pulse causes di/dt in Eq. (1-1) to be a constant.

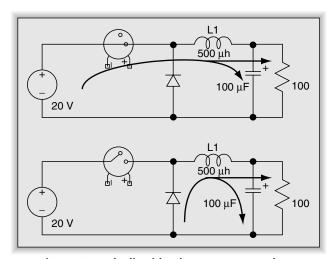

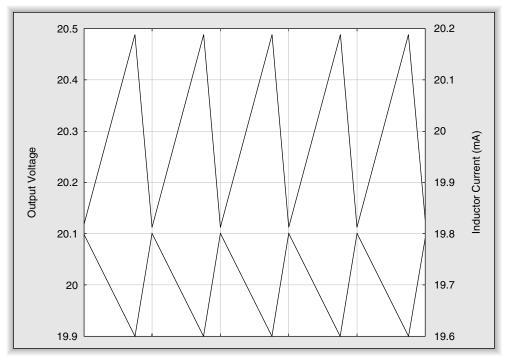

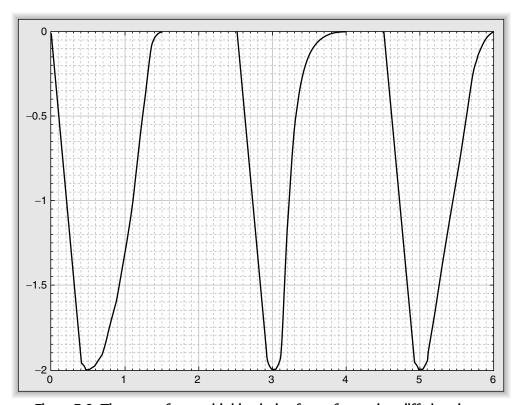

Figure 1-2 shows a plot of the output voltage (lower trace) and inductor current (upper trace) after the system is at steady-state providing 5 V and 500 mA to the load resistor.

Note that the change in output current is relatively small compared to the DC value of current in the inductor. In this case, the ripple current is 75 mA P-P. Another important point is that the ripple current is independent of load current when the system is steady-state. This is a consequence of the current through the inductor being controlled by the voltage across the inductor. The slope and duration of charging is controlled entirely by the difference  $(V_{in} - V_{out})$ . The average inductor current is equal to the output current.

It is also possible for the buck converter to work in discontinuous mode, which means the inductor current goes to zero during part of the switching period.

Figure 1-2: Output voltage and inductor current in a buck regulator

Equation (1-6) does not hold for discontinuous operation. The output ripple voltage is higher for a buck converter in discontinuous mode because the capacitor must supply the load current during the time that the inductor current is zero. Usually, a buck converter only runs in discontinuous mode when the load current becomes very small compared to the design current.

### **Boost Converter**

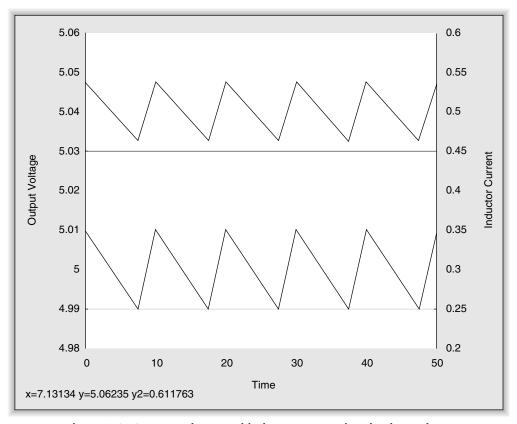

Figure 1-3 shows an ideal boost converter regulator made of an ideal voltage source, an ideal switch, an ideal diode, an ideal inductor, a capacitor, and a load resistor. It is called a boost converter because the voltage across the inductor adds to the input supply voltage to boost the voltage above the input value. The output of a boost converter is always greater than the input voltage. This ideal

regulator is designed to use a 5 V source and provide 20 V to the 1000 ohm load. The diode provides a path for the current once the switch is opened. The diode is off while the switch is closed. The switch is opened and closed once every  $10~\mu s$ .

The switch and voltage source provide current to charge the inductor with energy while the switch is closed. While the inductor is charging, the current in the load is supplied by the capacitor because the diode is reverse biased. When the switch opens, the current in the inductor continues to flow, but now the inductor current forward biases the diode and flows through the load circuit. The voltage across the inductor reverses and adds to the voltage of the input supply. When the regulator is at steady-state, the output voltage is:

$$V_{out} = V_{in}/(1 - Duty Cycle)$$

(1-7)

This equation is independent of the value of the inductor, the load current, and the output capacitor for continuous mode operation.

Boost converters require much more capacitance than a buck converter because the capacitor supplies all of the load current while the switch is closed.

Figure 1-4 shows a plot of the output voltage (lower trace) and inductor current (upper trace) after the system is at steady-state providing 20 V and 20 mA to

Figure 1-3: Idealized boost converter regulator

Figure 1-4: Output voltage and inductor current in a boost regulator

the load resistor. Just as in the buck converter, the ripple current in the inductor is independent of the output current for continuous mode operation. Typically, the peak inductor current is only slightly larger than the average inductor current.

It is also possible to run a boost converter in discontinuous mode. Discontinuous mode results in larger ripple current for boost converters, just as in the buck converter, because the capacitor must supply load current while the inductor current is zero. The other consequence of discontinuous operation of boost converters is very large peak current in the switch and inductor.

You can calculate the input current in both modes for a given output current. In our continuous mode example in Figure 1-3, the input current averages 80 mA. Equation (1-8) gives average input current for both modes. Equation (1-9) gives peak input current for discontinuous operation.

$$I_{\text{in-avg}} = I_{\text{out-avg}} \left( \frac{1}{1 - \text{Duty Cycle}} \right)$$

(1-8)

$$I_{\text{in-peak}} = 2 * I_{\text{out-avg}} ((1 - (V_{\text{out}}/V_{\text{in}}))/\text{Duty Cycle}$$

(1-9)

If our example circuit had a duty cycle of 0.25 (discontinuous mode) instead of 0.75 (continuous mode), the peak inductor and switch current would be 480 mA instead of 81.75 mA.

# **Inverting Boost Converter**

Figure 1-5 shows the circuit of an ideal inverting boost converter. The switch and voltage source provide current to charge the inductor with energy while the switch is closed. While the inductor is charging, the current in the load is supplied by the capacitor because the diode is reverse biased. When the switch opens, the current in the inductor continues to flow, but now the inductor current forward biases the diode and flows through the load circuit. Since one side of the inductor is tied to the common point, the current flow when the switch opens causes a negative output voltage.

Figure 1-5: Idealized inverting boost converter

When the regulator is at steady-state, the output voltage is determined by Eq. (1-10) for continuous mode operation. Just as in the positive boost converter, the output voltage will be larger in magnitude than (or equal to) the input voltage.

$$V_{out} = -V_{in} * (Duty Cycle)/(1 - Duty Cycle)$$

(1-10)

## **Buck-Boost Converter**

If we add an additional switch and an additional diode to the boost converter as in Figure 1-6, we can create a buck-boost converter that will allow us to create a positive voltage that is either above or below the input voltage. Both switches close and open at the same time in this circuit. Again, the inductor is charged while the switches are closed and energy is delivered to the load when the switches open, just as it is in the boost converter. Diode D1 connects one end

Figure 1-6: Idealized buck-boost converter

of the inductor to the common point so the voltage across the inductor can be either above or below the input voltage.

# Transformer Isolated Converters

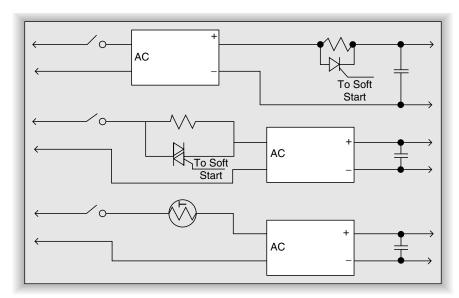

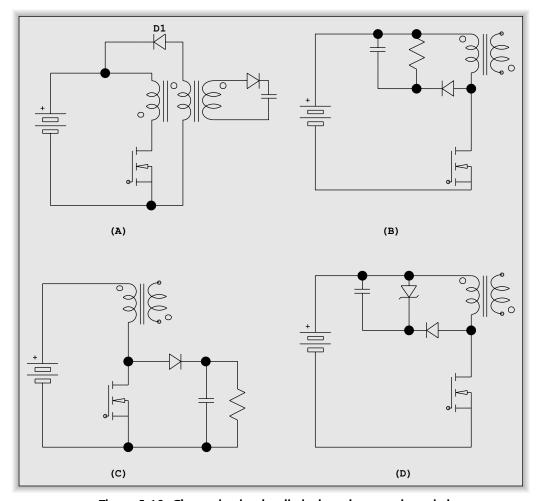

Power supplies that are intended to run directly from the AC power lines (off-line supplies) require a transformer to isolate the load side from the AC lines. Transformers can also be used in power supplies where isolation is required for other reasons such as medical equipment use. Table 1-1 lists power range and complexity versus appropriate converter type. This table gives a generally accepted range for each converter type. Each type can be used above or below these ranges, but the design problems to create an efficient supply become greater.

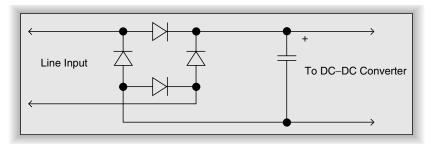

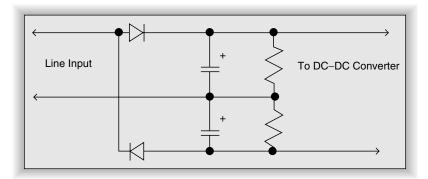

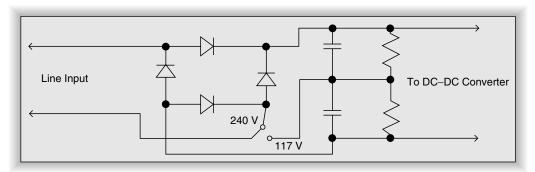

An off-line power supply is really a DC power supply that feeds a transformer iso-lated DC–DC converter. The rest of this section will focus on the DC–DC converter circuits. We will look in detail at the input DC power supply in Chapter 3.

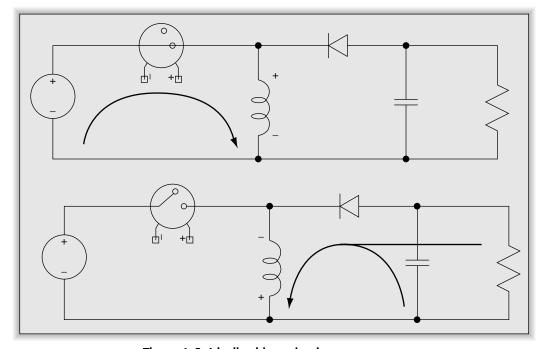

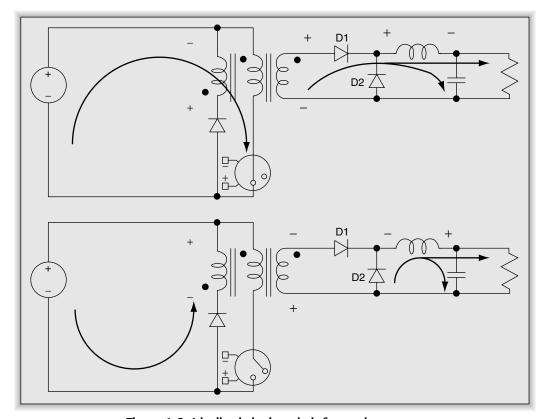

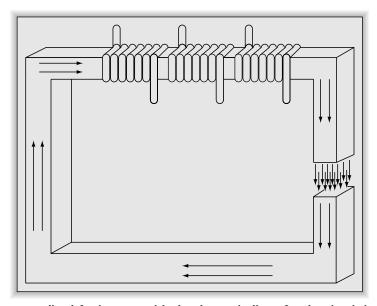

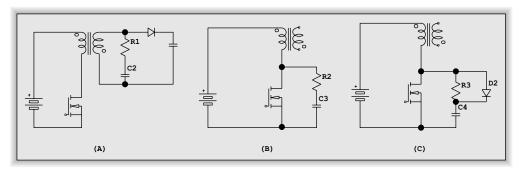

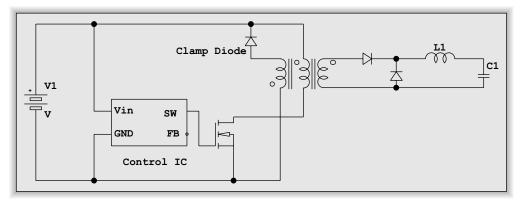

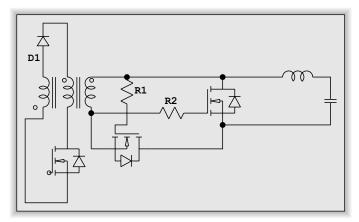

Figure 1-7 shows a single switch flyback converter. It appears that this supply uses a transformer, but, in fact, the magnetic component is an inductor with two windings. This supply uses the primary winding of the inductor to store the magnetic energy in the same way that the boost converter works. Note that the phasing of the windings is opposite to normal transformer use. While the switch is closed, the energy is stored in the core and no current flows in the secondary. When the switch opens, current flows in the secondary [as required by Eq. (1-1)] and delivers energy to the load. The voltage on the output is determined by the turns ratio, just as in an actual transformer. The flyback converter is the only off-line converter that uses an inductor; all others use a transformer. One advantage of the flyback converter is that there is no need for

**Table 1-1:**

| Circuit     | Power Range | Relative complexity |

|-------------|-------------|---------------------|

| Flyback     | 1W-100W     | Low                 |

| Forward     | 1W-200W     | Medium              |

| Push-Pull   | 200W-500W   | Medium              |

| Half Bridge | 200W-500W   | High                |

| Full Bridge | 500W-2000W  | Very high           |

Figure 1-7: Idealized single switch flyback converter

an additional smoothing choke. The energy stored in the inductor is dumped directly into the capacitor and the load. This is also a disadvantage because the current for the load is supplied by the capacitor alone while the inductor is charging. The ripple voltage is larger for the flyback converter unless a larger output capacitor is used.

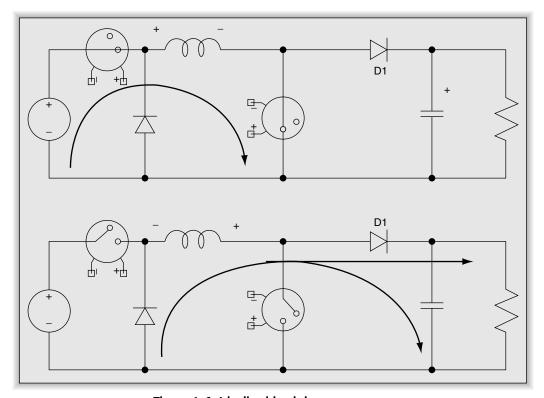

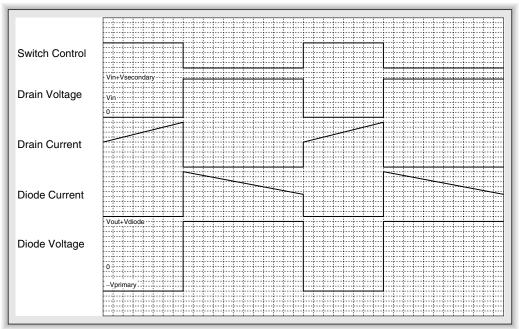

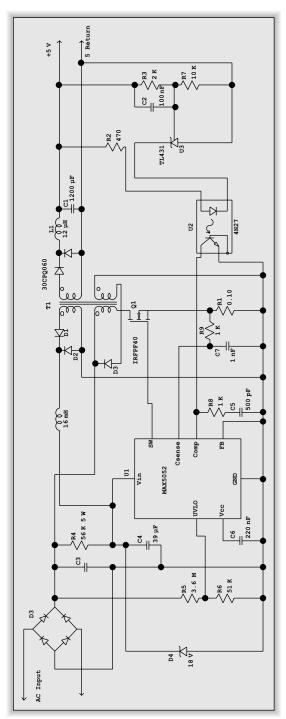

Figure 1-8 shows a single switch forward converter. During the time the switch is closed, current flows in the primary and in the secondary. The secondary current charges the filter choke just as in a buck converter. When the switch opens, current must continue to flow in the choke, as described in Eq. (1-1). The commutating diode (D2) in the secondary acts just as it does in the buck converter and allows inductor current to continue to flow.

Real transformers also have parasitic inductance that looks like an inductor in series with the primary of the transformer. The primary current that is flowing in the parasitic inductance must continue to flow according to Eq. (1-1) when the switch opens. When the switch opens, current stops flowing in the primary winding and in the secondary winding. The clamp winding (the left one) is phased opposite to the primary and secondary so when the current stops flowing, current begins to flow in the clamp winding as the flux decreases. The current flow in the clamp winding resets the flux in the transformer core to its resting value for the next pulse. The clamp winding acts exactly like the secondary winding of a flyback converter and delivers the energy of the parasitic inductance back to the input supply. There are other mechanisms of resetting the flux in the core, which we will explore in Chapter 5.

Figure 1-8: Idealized single switch forward converter

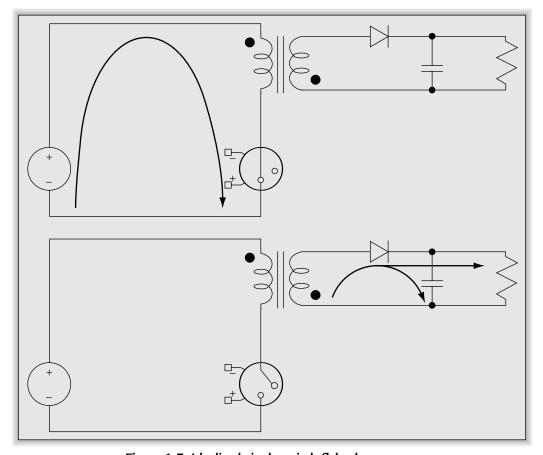

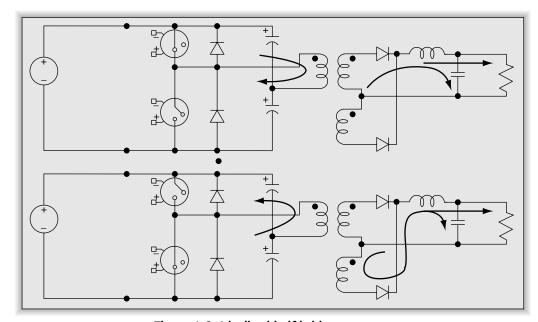

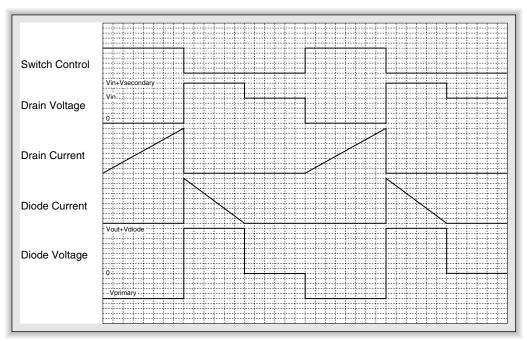

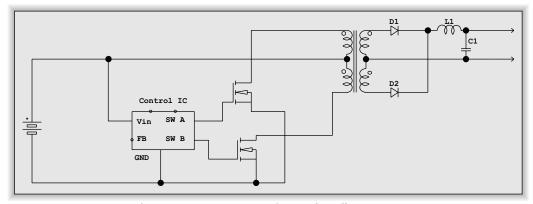

Figure 1-9 shows a half bridge converter. This circuit is a high voltage equivalent of a TTL totem-pole output. The switches conduct alternately, which produces a bipolar voltage across the transformer primary. This requires that we have a full wave rectifier for the output. A clamp winding is not necessary since the opposite phase output diode will allow the current to flow in the secondary winding. We can add freewheeling diodes to the primary to control the voltage present on the secondary when the switches open. The capacitors provide a voltage divider that sets one end of the primary winding to one-half the input voltage. These capacitors are almost always part of the input DC power supply, so they perform the dual functions of voltage divider and input charge reservoir.

Figure 1-10 shows a full bridge converter. This design uses four switches to alternate the direction of current through the core.

Figure 1-11 shows a push-pull converter. The switches open and close 180 degrees out of phase, just as in a class B push-pull audio amplifier. Push-pull converters are rarely used in off-line supplies because they require high voltage transistors and it is very difficult to control the flux in the transformer. Modern

Figure 1-9: Idealized half bridge converter

Figure 1-10: Idealized full bridge converter

Figure 1-11: Idealized push-pull converter

current mode PWM controllers have made using push-pull circuits practical in low voltage circuits.

# Synchronous Rectification

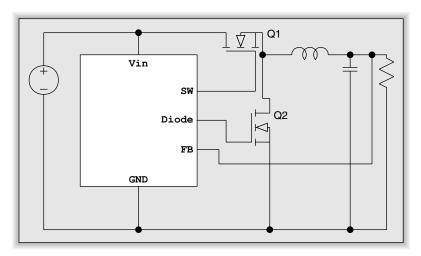

In all of the circuits we have reviewed in this chapter, we have used diodes as voltage-controlled switches. When they are reverse biased, they act as open switches. When they are forward biased, they act as closed switches. Power MOSFETs also work as switches. When the gate to source voltage is sufficient to turn on a MOSFET, current can flow in either direction through the transistor. Power MOSFETs that are used as switches can have on resistance of 0.01 ohm or less. A Schottky diode that is conducting 5 A will drop approximately 0.4 V and dissipate 2 W. A power MOSFET with 0.01 ohm on resistance will dissipate 0.25 W while conducting 5 A. This is a sizeable increase in efficiency. Figure 1-12 shows a buck regulator using synchronous rectification and ideal passive components. This circuit uses an ideal buck converter controller that sequences the MOSFETs and provides the voltage feedback control. When Q1 is on, the circuit turns off Q2. When Q1 is turned off, Q2 is turned on. While this example shows a buck converter, with proper drive circuitry it is possible to replace diodes with MOSFET switches in all designs.

Figure 1-12: Buck converter using power MOSFETs as switches instead of diodes

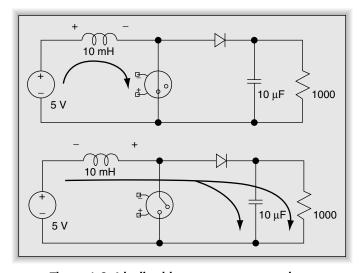

# Charge Pumps

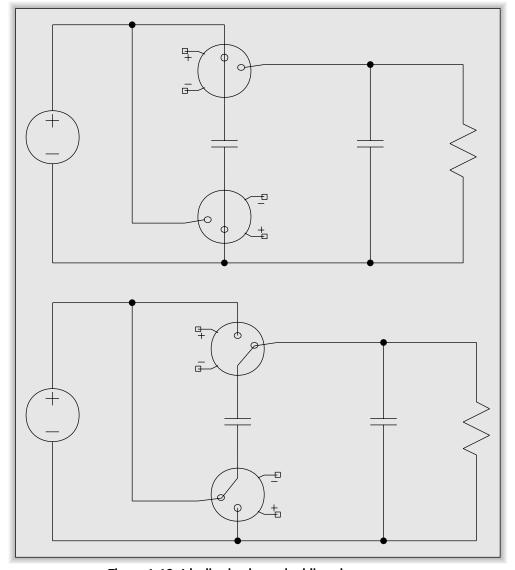

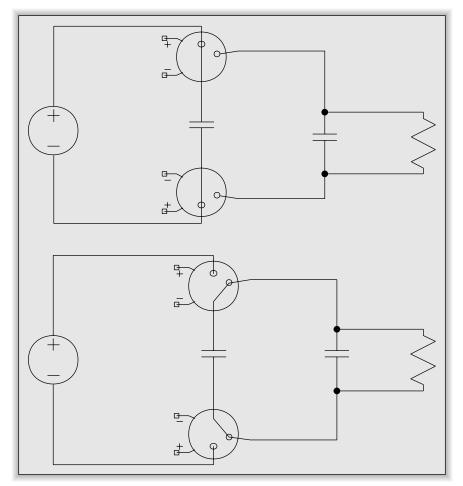

Charge pumps use a capacitor to either increase or invert the input voltage. An ideal voltage doubling charge pump is shown in Figure 1-13. The charge pump capacitor is called a *flying* capacitor (presumably because the switches resemble flapping wings as they change state). During charging, the flying capacitor

Figure 1-13: Idealized voltage doubling charge pump

is charged by the switches. Then the capacitor is connected to the load in series with the input supply to provide a voltage above the input.

Figure 1-14 shows a different arrangement of the switches that allows a charge pump to provide a negative voltage nearly equal in magnitude to the input voltage.

Charge pumps are typically used in applications where a low current is necessary, such as in a bias supply for an IC or a FET amplifier. Charge pumps are not able to supply large amounts of current without using large value capacitors. The practical limit to output current is approximately 250 mA.

A voltage multiplier circuit is also a form of charge pump. Figure 1-15 illustrates a traditional voltage multiplier circuit driven by a totem-pole switch square wave generator. This circuit uses the diodes as switches to steer the current from the generator to the output capacitor.

Figure 1-14: Idealized voltage inverting charge pump

Figure 1-15: Square wave driven voltage multiplier

Figure 1-16 shows a step-down charge pump. This circuit varies the duty cycle to allow the output voltage to be less than the input voltage. The circuits of Figure 1-16 and Figure 1-14 will have an output voltage magnitude that is less than the input voltage. Not all of the energy stored in the flying capacitor can be transferred to the output capacitor. The switching action behaves like an equivalent resistance that depends on the switch frequency and the relative values of the capacitors. We will look at this in detail in Chapter 2.

Figure 1-16: Idealized step-down charge pump

# CHAPTER 2

# **Control Circuits**

- Basic Control Circuits

- The Error Amplifier

- Error Amplifier Compensation

- Test Sequence

- A Representative Voltage Mode PWM Controller

- Current Mode Control

- A Representative Current Mode PWM Controller

- Charge Pump Circuits

- Multiple Phase PWM Controllers

- Resonant Mode Controllers

## **Control Circuits**

We will explore the various forms of controllers available from semiconductor manufacturers. There is a large variety of controllers available, but each part is usually intended for a narrow application. I will refer to application notes from various manufacturers. These are available on each manufacturer's website or by contacting the manufacturer.

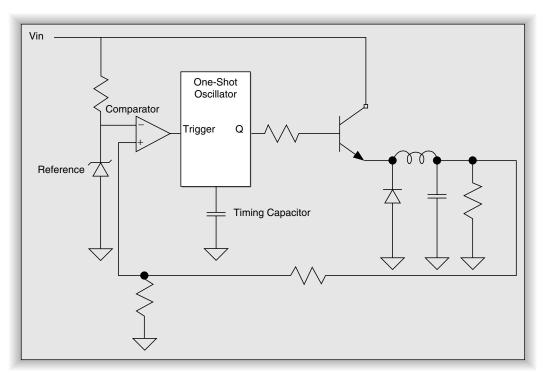

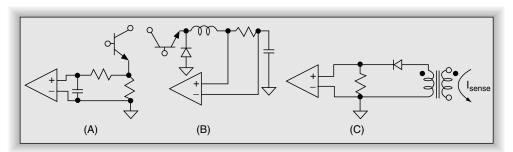

#### **Basic Control Circuits**

The simplest form of control circuit is variable frequency/constant on-time or Pulse Frequency Modulation (PFM). In Figure 2-1, the oscillator has a constant on-time (basically a one-shot multivibrator similar to a 555 timer). As soon as the control voltage drops below the reference, the oscillator is triggered to turn on by the comparator. Under light loads, the frequency is low and the duty cycle is low. As the load increases, the frequency increases. The maximum frequency occurs at 50% duty cycle. The wide range of ripple frequency can cause problems for electromagnetic compatibility (EMC) and for ripple control on the output. The Texas Instruments TL-497 is a popular commercial example of this type of circuit.

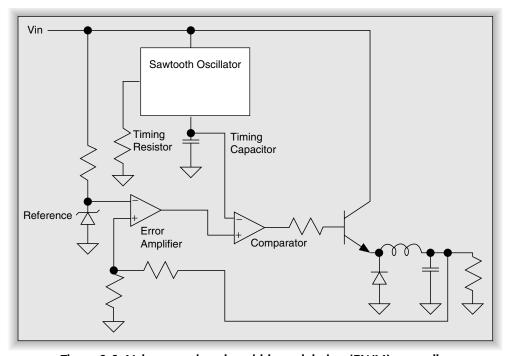

EMC and ripple control are much more predictable and controllable if a constant frequency is used and the width of the pulse is varied. Pulse width modulation (PWM) uses a constant frequency and varies the on-time of the switch. Figure 2-2 illustrates the basics of a voltage mode PWM controller.

The voltage divider is used with the error amplifier and reference voltage to generate a scaled error signal. The oscillator is similar to a 555 oscillator and generates a constant frequency sawtooth wave. Typically, the timing resistor

Figure 2-1: Pulse frequency modulation circuit

Figure 2-2: Voltage mode pulse width modulation (PWM) controller

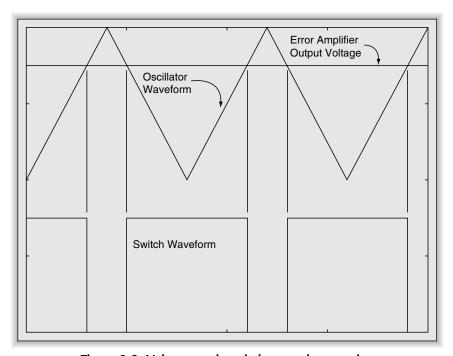

sets the charge current for the timing capacitor. Once the voltage on the timing capacitor reaches the trip point, a flip-flop in the oscillator turns on and rapidly discharges the timing capacitor to the lower trip point. The output switch is driven by comparing the error voltage and the oscillator voltage. Figure 2-3 shows how the switch signal is generated.

When the oscillator voltage is less than the error amplifier output voltage, the switch turns on. When the oscillator voltage goes above the error amplifier output voltage, the switch turns back off. If the error voltage is less than the lowest triangle voltage, the duty cycle will be 100%; if the error voltage is greater than the highest voltage of the triangle voltage, the duty cycle will be 0%.

Flyback and boost converters require a minimum amount of off-time so that energy stored in the inductor can be dumped to the output circuit. Some forward converter designs will also require a guaranteed amount of off-time. Modern voltage mode PWM controllers provide a mechanism to ensure a duty cycle less than 100%. This dead time is usually adjustable with an external resistor.

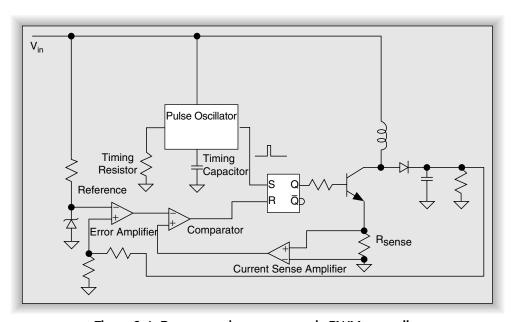

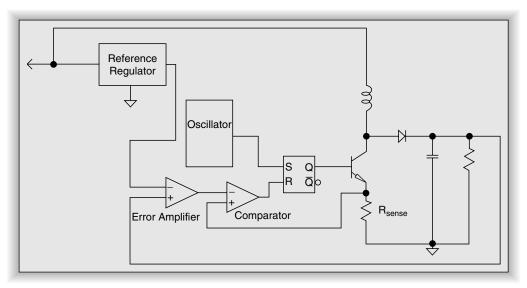

Figure 2-3: Voltage mode switch control generation

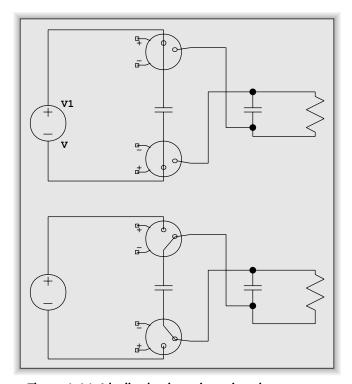

Current mode PWM control has inherent advantages over voltage mode control. These include improved transient response and a simpler control loop. Figure 2-4 illustrates the basics of a current mode PWM controller. In this circuit, the oscillator runs at a constant frequency. The pulse from the oscillator sets the flip-flop, which starts current flowing in the transistor switch. The current flow in the switch stops when the current as measured by R<sub>sense</sub> creates a current sense voltage that equals the trip point set by the error amplifier. The comparator resets the flip-flop, which shuts off the switch. The error amplifier is used to adjust the trip point for the switch current so that the inductor current is the proper amount to maintain the output voltage. As the output voltage approaches the desired value, the error signal reduces the current trip point to maintain a constant average inductor current.

#### The Error Amplifier

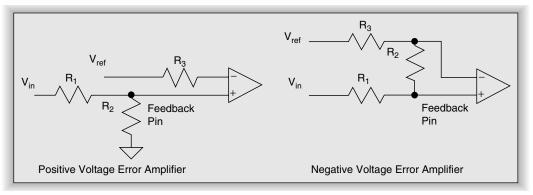

Figure 2-5 shows the typical methods of setting up the error amplifier to control the output for a positive output supply and for a negative output supply. The negative output circuit uses a voltage divider connected to the reference to

Figure 2-4: Representative current mode PWM controller

Figure 2-5: Positive and negative voltage error amplifiers

place the input to the amplifier above ground. PWM circuits are intended to operate from a single positive power supply. This means that all of the pins, especially the error amplifier and current sense pins, must not go more than one diode drop below ground.

You will also notice that there is a resistor  $(R_3)$  on the pin opposite the feedback pin. All bipolar transistor difference amplifiers (including op-amps and comparators) use the base of a transistor as the input. The input transistors require a small amount of bias current in order for amplification to occur. This bias current flows in  $R_1$  and  $R_2$  in addition to the normal voltage divider current, and it slightly changes the voltage at the feedback pin. The small amount of additional DC voltage due to the bias current will cause a small offset in the output voltage that depends on the closed loop gain of the amplifier and the values of  $R_1$  and  $R_2$ .  $R_3$  has a value equal to the parallel equivalent of  $R_1$  and  $R_2$ . This ensures that both amplifier input pins are raised above ground by the same amount to balance the effects of the input bias current.

The output of the error amplifier is similar to a resistance-coupled DC circuit. Instead of a resistance, the load for the output transistor is a current source. The effect is that the current is split between the output transistor and the load. This is the equivalent of an open collector digital circuit, except that the transistor is operated in the linear region. Several "open collector" circuits can have their outputs connected together just like a wired-OR open collector digital circuit. The circuit that pulls the output to the lowest voltage is the one that controls

the voltage at the input to the PWM comparator. The current source load for the output transistor makes it a transconductance amplifier rather than a voltage amplifier. The voltage gain is equal to the transconductance times the load resistance.

#### **Error Amplifier Compensation**

There is a broad class of electronic systems covered by classic feedback control theory. Closed loop op-amp circuits, electromechanical servos, phase locked loops, linear power supplies, and switching power supplies can all be analyzed using control theory. A detailed description of feedback theory is beyond the scope of this book. Thomas Frederiksen gives a very good description of the effects of the transfer function in Chapter 4 of his book *Intuitive IC Op Amps* (National Semiconductor Technology Series, 1984). He describes how multiple poles and zeros can ensure stability or lead to oscillations in a closed loop system. There is also a condensed general description of frequency compensation of amplifier/power amplifier combinations at the end of Linear Technology Application Note 18. Consult a control theory textbook for a complete understanding of compensation.

The error amplifier in PWM controllers is not the equivalent of a 741 or 1458 op-amp. Op-amps have internal compensation that places a low frequency pole somewhere below 100 Hz (usually under 5 Hz). This pole dominates the overall closed loop amplifier performance by rolling off the gain as frequency increases. The error amplifier in PWM controllers usually has no internal compensation. PWM controllers bring the output of the error amplifier out to a pin so that poles and zeros can be added to the closed loop system to provide frequency compensation to the system.

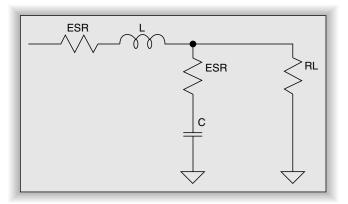

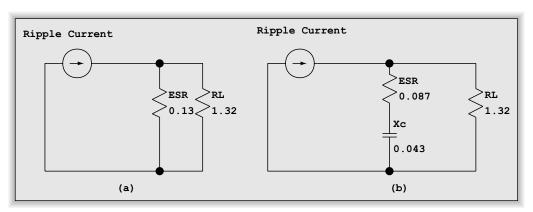

Numerous effects in a switching power supply tend to increase the phase delay around the loop. Two major contributors are the inductor and the filter capacitor, including its equivalent series resistance (ESR). The combination of the inductor and capacitor in the output circuit are the equivalent of a series resonant circuit and will cause two complex poles in the response. The transfer function changes with changes in the load current and power line voltage. The output capacitor and its ESR form a zero, and the load and output capacitor

create a pole. Figure 2-6 shows the equivalent circuit of the output capacitor, ESR, and load resistance. You will notice that ESR is a contributor to both the pole and the zero.

The goal of compensation is to ensure that the final power supply will have a quick response to load and input transients, and will not oscillate.

Compensation that is heavily damped will guarantee that the output voltage will not oscillate, but the output will likely have a large, long-lasting transient response to rapidly changing input or output. It is also likely to result in significant overshoot during recovery from short circuits. Response that is too rapid will result in oscillations in the control loop.

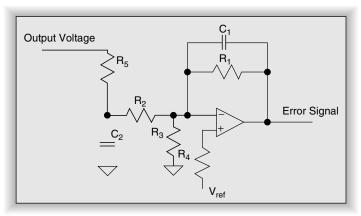

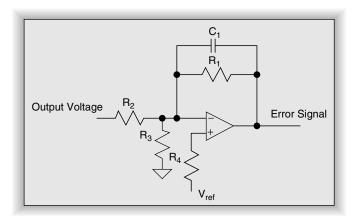

Figure 2-7 shows a typical compensation network for a buck or forward converter. The resistor and capacitor add a pole to the transfer function. This compensation network needs to be optimized for both gain and frequency. The resistor and capacitor act as a damper to lower the Q of the circuit.

Figure 2-8 shows a typical compensation circuit for a continuous mode boost or flyback converter. All continuous inductor current boost and flyback converters have a zero in the right-half plane. This requires the second pole added to the feedback response. This pole must roll off gain below the frequency of the right-half plane zero. Poles and zeroes in the right-half plane are associated with responses that are steadily increasing in the time domain. The effect of this zero is obvious if you run a simulation of the startup of a boost converter without the second pole. The output voltage will have tremendous overshoot.

Figure 2-6: Equivalent series resistance in filter inductor and capacitor

Figure 2-7: Typical compensation circuit for a buck or forward converter

None of the application notes from IC manufacturers gives a rigorous method of evaluating the response of a switching supply using a mathematical approach. Application Note U-95 from Texas Instruments gives some guidance on math for linear power supply compensation that can be used for switching power supply analysis. However, if you understand the math involved, you probably don't need this book.

I prefer the empirical method described in Linear Technology Application Notes 19 and 25 for ensuring that the compensation circuit is optimal for the design. This approach uses time domain analysis rather than frequency domain analysis. The description in these application notes is specific to the LT1070

Figure 2-8: Typical compensation circuit for a continuous mode boost or flyback converter

series of current mode controllers, but the technique is applicable to all switching power supplies that have transconductance error amplifiers.

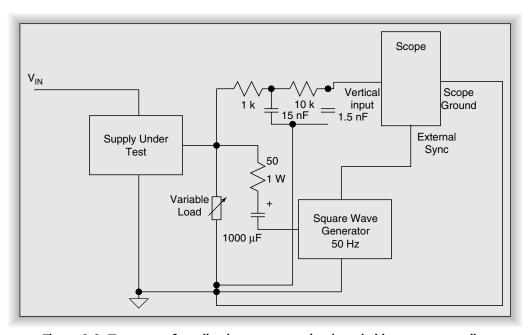

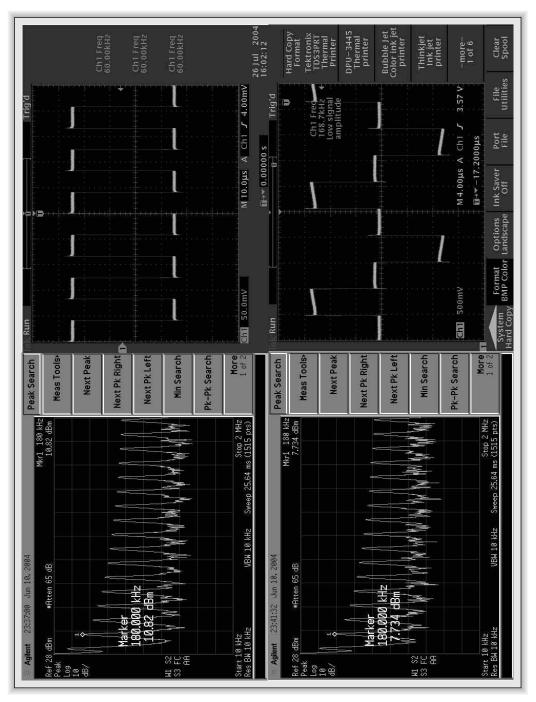

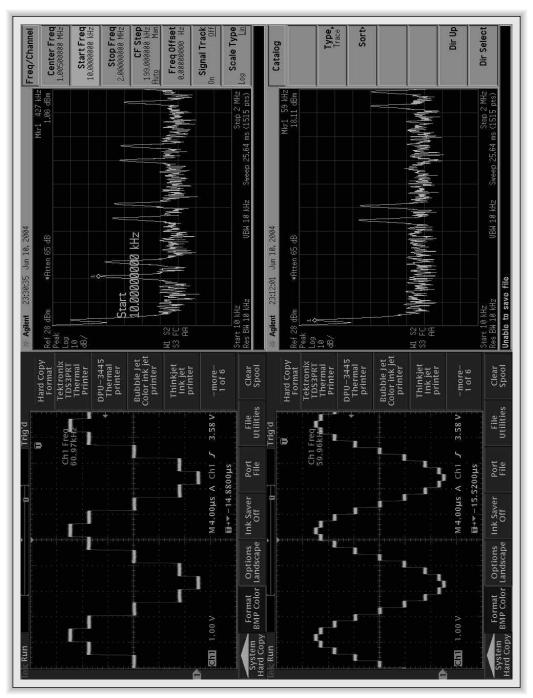

Figure 2-9 shows a test setup based on Linear Technology application notes. There are three pieces of test equipment required. The first is a variable load. This can be an active load that is adjustable or simply a set of high power resistors. The second is an oscilloscope for observing the transient response of the power supply. The last is a function generator that will introduce step changes to the load. We are only interested in the step response, so we place a low-pass filter between the supply output and the input channel of the scope. Thus, we only see the DC value and not any switching frequency energy. We trigger the scope with the output of the function generator.

#### **Test Sequence:**

1. Start compensation with a resistance of 1 k $\Omega$  and capacitance of 2  $\mu F$ . This will load the error amplifier for high frequencies and create a dominant pole due to the capacitance and the load of the PWM circuit. There will be a zero in the response due to the resistance but it will have very little effect.

Figure 2-9: Test setup for adjusting compensation in switching power supplies

2. Verify that there are no ground loops by connecting the scope channel 1 probe to the ground connection. If channel 1 shows any response, you must isolate the scope or signal generator by breaking the safety ground connection. In order to maintain safety, you should use an isolation transformer between the test equipment and the power line.

Remember that breaking the electrical safety ground defeats the safety aspect of having a ground. You must use appropriate caution around the test equipment.

- 3. Adjust the signal generator for a 5 Vp-p square wave. This gives a 100 mA step input to the control loop. If the positive and negative step responses are not identical with light loading, reduce the signal generator voltage.

- 4. Verify that the response is a single pole "over-damped" response. If the response is not over-damped, increase the value of the resistor. The resistor should be increased first and then the capacitor value to ensure that we start with an over-damped condition.

- 5. Reduce the capacitor 2:1 per step until the response is slightly under-damped. This moves the pole frequency higher and increases the gain-bandwidth.

- 6. Start increasing the resistor value in 2:1 increments to decrease the response time and to increase damping. Stop when the response becomes overdamped again. Increasing this resistance moves the zero lower in frequency so that it starts to flatten out the gain response to mid-frequencies.

- 7. Continue to iterate, reducing both the capacitor and the resistor to give a fast damped response. The goal is to get the largest resistance and smallest capacitance that do not produce oscillations while giving rapid settling to the proper output voltage.

- 8. Now we have to verify that we have enough gain and phase margin over all conditions. One of the toughest problems is the value of the zero caused by the output capacitor and its ESR. ESR is very temperature-dependent. If the supply must operate at very low temperatures, the ESR will increase by

orders of magnitude. The margin test will entail testing the response to ensure no oscillations for all combinations of temperature, load, and input voltage. A good rule of thumb is to adjust for slight over-damping at the temperature extremes to ensure stable operation over the entire temperature range.

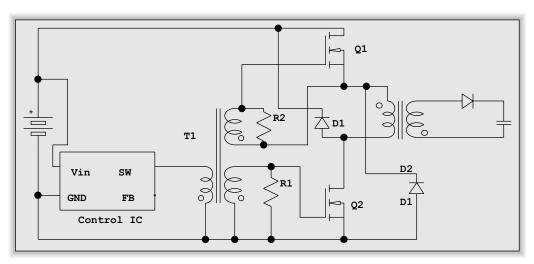

#### A Representative Voltage Mode PWM Controller

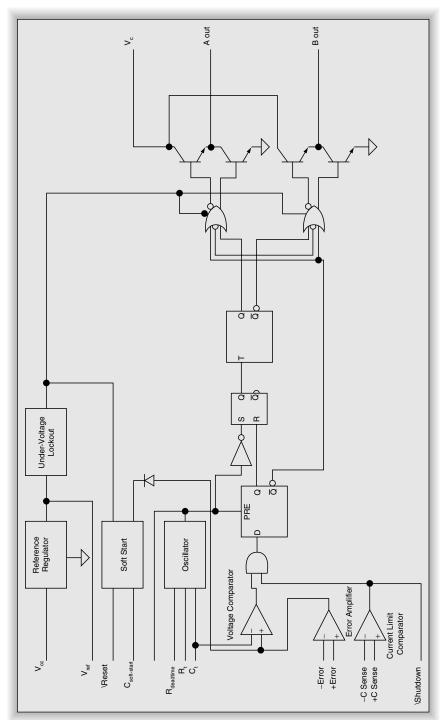

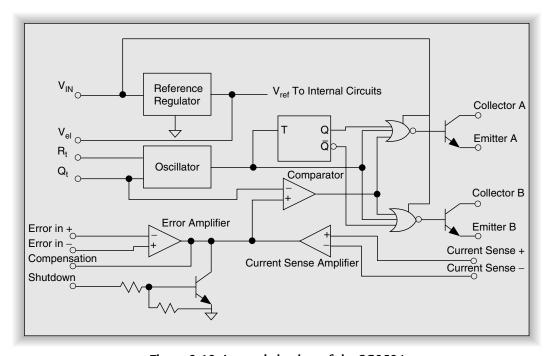

The 1526A family is representative of a second-generation, full-featured voltage mode PWM controller. This part is suitable for either DC–DC converter service or as an off-line controller at frequencies up to about 100 kHz. This part is especially suited to push-pull, half-bridge, and full-bridge circuits because it has two outputs. Figure 2-10 shows the internal block diagram of the controller.

The internal circuitry requires a stable, regulated voltage for proper operation. The reference regulator is a precision temperature-compensated linear regulator. It is capable of providing 20 mA to external circuits. The reference has a 2 V dropout, so the minimum supply voltage is 7 V. In the 1526A, the band gap reference is trimmed to make the final reference voltage accurate to  $\pm 1\%$ .

The under-voltage lockout circuit compares the reference voltage to an internal band gap reference. The circuit pulls the reset pin low, disables the output drivers, and clamps the error amplifier output through the diode so there is no possibility of spurious output pulses until all of the circuitry has sufficient voltage for proper operation. The lockout continues until the reference voltage reaches 4.4 V. The lockout comparator has 200 mV of hysteresis. The circuit will not lock out once the reference reaches 4.4 V until the reference falls below 4.2 V. This prevents noise from causing spurious reset if the reference voltage is rising slowly.

Once the reset pin is released by the under-voltage lockout circuit, the normal soft start sequence begins. The soft start capacitor is connected to the error amplifier output through a clamp transistor that limits how high the error amplifier output voltage can rise during soft start. The clamp on the error voltage limits the maximum pulse width. As a consequence, the increase in inductor current and the rate of rise of output voltage while the system is starting is limited. The clamp is no longer active once the capacitor charges to 5 V. The soft start

Figure 2-10: Internal block diagram of the 1526A voltage mode PWM controller

capacitor is charged with a constant current of  $100 \mu A$  (typical), so we can use the capacitor definition and current definition to find the soft start time.

$$Q = C*V \text{ and } I = \Delta Q/\Delta t$$

(2-1)

If we differentiate both sides of the capacitor equation we get

$$I = C * \Delta V/\Delta t \tag{2-2}$$

I is a constant 100  $\mu$ A and  $\Delta V$  is 5 V (from reset to fully charged), so we can find the relationship between capacitance and time by rearranging Eq. 2-2.

$$C/\Delta t = 100 \,\mu A/5 \,V = 20 \,\mu F/s$$

(2-3)

This value is an approximation because the charging current can vary from  $50 \,\mu\text{A}$  to  $150 \,\mu\text{A}$ . Also, the normal control loop will begin to dominate the operation of the system long before the capacitor is fully charged.

Soft start is necessary because the current in the inductor is large when the full input supply voltage is across it. It is quite probable that the combination of output capacitor and choke inductance will allow the current to increase so quickly that the output voltage can overshoot the intended voltage by hundreds of millivolts or even several volts. The purpose of the soft start circuit is to protect the diodes and switch transistors from excessive currents during startup and to provide a damped response to the very large transient at startup.

The oscillator in the 1526A provides a dead time control pin in addition to the normal timing resistor and timing capacitor pins. If the R<sub>D</sub> pin is grounded, the dead time is controlled by the discharge circuit in the oscillator. Adding a resistor from the R<sub>D</sub> pin to ground will increase the dead time. The data sheet lists an increase of 400 ns/ohm when operating at 40 kHz. The data sheet does not give design information for other frequencies, so the value of R<sub>D</sub> will need to be determined experimentally. It is obvious from this part of the data sheet that the 1526A was designed when 20 kHz supplies were state of the art. We would want to increase the dead time for push-pull or bridge circuits where we are using slow bipolar transistors as switches. Bipolar switches store charge in the base-collector junction that must be recombined before the transistor will shut off. Increasing dead time ensures that one transistor has completely turned off before the alternate transistor begins to conduct.

The oscillator also has a sync pin that allows the oscillator to be synchronized to an external oscillator or to sync another controller. Some systems contain multiple PWM controller circuits. The sync pin allows all of the controllers to maintain exact frequency and phase so that circuits can be paralleled. The master 1526A is programmed with  $R_T$ ,  $R_D$ , and  $C_T$  for the proper frequency. All of the slave 1526 parts share the sawtooth waveform by connecting all  $C_T$  pins together. All of the sync pins must also be connected together. All of the slave  $R_T$  pins are left open.

The sync pin could also be used to sync the controller to an external logic clock if the system requires. To sync to an external logic signal, you must set the oscillator frequency approximately 10% below the desired frequency. The logic circuit should supply a short pulse (on the order of 500 ns) to the sync pin. This short pulse terminates the charge phase of the oscillator and restarts the cycle.

The sync pin, reset pin, and shutdown pin are all bidirectional, low active logic pins. Figure 2-11 shows how the internal circuits drive the pin as an open-collector output with internal pullup and as an input to the internal circuits. The shutdown pin can be used for fault conditions that require an immediate shutdown of the controller. The shutdown pin doubles as an output indicating

Figure 2-11: Internal circuitry of bidirectional pins in 1526A

that the current limit comparator is active. Pulling the shutdown pin low disables the output drivers. The reset pin discharges the soft start capacitor and clamps the error amplifier output. Releasing the reset pin will initiate a soft start cycle. Each of these pins is compatible with TTL or CMOS logic.

The 1526A implements digital current limiting. The current sense comparator provides a logic output that terminates the output pulse. This allows the system to terminate each output pulse if the current limit is exceeded. Do not confuse this operation with current mode PWM control where the error signal controls the current trip point. This part has a fixed threshold for current limit action. The current sense amplifier has an internal 100 mV reference on the inverting pin, so the inverting pin can be grounded to provide for unipolar current sense input. This allows for a very low resistance current sense to minimize current sense power loss.

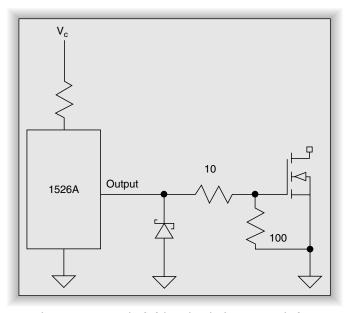

Other circuits, such as the SG2524, use a difference amplifier that subtracts voltage from the output of the error amplifier and reduces the pulse width output. The internal circuit of the SG2524 is shown in Figure 2-12.

Figure 2-12: Internal circuitry of the SG2524

The 1526A PWM pulse generator uses digital logic to ensure that the comparator does not produce multiple pulses because of noise. The PWM comparator compares the oscillator ramp voltage to the error amplifier voltage and sends a pulse to set the flip-flop when the voltages are equal. The high signal from the PWM latch is sent to the output steering logic. The output pulse is terminated when the oscillator discharge pulse resets the PWM latch.

The output steering logic performs three functions. The first function is implemented by a toggle flip-flop that steers alternate output pulses to alternate output drivers. This allows the 1526A to be used in symmetric drive circuits such as push-pull or bridge circuits. The second function is output blanking. There is a minimum dead time on each output that is controlled by the length of the oscillator reset pulse. The output blanking is ANDed with the pulse command from the PWM latch so that it overrides the PWM latch signal. The third function of the steering logic disables the output drivers for fault conditions such as over-temperature and any time the reset pin is active.

The 1526A has two totem-pole outputs that can be connected to a power supply that is different from the control circuit power supply. This allows the drive to be tailored to the external switches. Each of the outputs is driven at one-half of the oscillator frequency. The pulses from the two outputs do not overlap. When the output is driven low, it saturates the lower transistor. There is a small amount of time where both transistors are on (cross-conduction time) because of the turn-off delay caused by saturation in the lower transistor. Because of the cross-conduction current, this device needs a small resistor in series with the  $V_{\rm C}$  pin to limit the current. The 1526A is an improved version of the 1526 and limits the cross-conduction time to 50 ns. This length of time still requires the current limit resistor.

Figure 2-13 shows a typical drive circuit for FET switches. The 1526A output transistors can source or sink 100 mA. The capacitance of the FET can draw substantial current during charge and discharge. The resistor in series between the FET gate and the output pin protects the output transistors by limiting the peak current. Additionally, the drain to gate capacitance is usually quite large and can couple large inductive voltage transients from the drain circuit into the gate circuit. The Schottky diode ensures that the voltage on the output pin cannot be driven more than 0.3 V negative with respect to the IC ground pin.

Figure 2-13: Typical drive circuit for FET switches

#### **Current Mode Control**

Figure 2-14 shows the basic circuit of a current mode PWM controller in a boost converter. This circuit has two control loops. The outer loop measures the output voltage and provides an error signal to the inner loop. The inner loop compares the error signal and an analog of the inductor current to decide when to turn off the switch. The effect is to change the pulse width. The pulse width is a function of the inductor current rather than a function of the error signal.

The oscillator starts each cycle by setting the output latch to turn on the switch. The error amplifier generates the error signal that is used to compare against the inductor current signal. Once the peak inductor current signal is equal to the error signal, the comparator resets the latch and turns off the switch. If the output voltage decreases, the error signal will increase and allow the peak current to increase with the next pulse.

The operation of the current mode controller has advantages over a voltage mode controller. The first is that the inductor current is a direct function of the error voltage, so for small signal analysis the inductor can be replaced by a

Figure 2-14: Basic circuit of a current mode PWM controller

voltage controlled current source. This removes one order from the transfer function. The control loop is easier to compensate than a voltage mode circuit. Another advantage is that input line voltage changes are removed from the compensation problem. The peak current through the inductor is a function of the voltage across the inductor. If the input voltage drops, it will just take longer for the inductor current to rise to the required value and for the comparator to shut off the switch.

Current mode controllers are not without their problems. Whenever the duty cycle exceeds 50% and inductor current is continuous, current mode controllers have a response called subharmonic oscillation. The inner current loop is unconditionally stable as long as the duty cycle is below 50%. When the duty cycle is larger than 50%, the output will diverge from stable control when the inner loop is perturbed by noise or transients. The average inductor current will stay in control and be set by the error amplifier, but it will vary at subharmonics of the switch frequency. For a 40-kHz switch frequency, the inductor current will have frequency components at 20 kHz, 10 kHz, etc. These subharmonic frequencies can produce audible responses in the inductor and other components. A current mode controller can be stabilized to maintain control by adding slope

compensation. Slope compensation is usually accomplished by feeding some of the voltage from the oscillator capacitor into either the current sense amplifier or the error amplifier. Slope compensation changes the current trip from a constant voltage to a sawtooth waveform at the switch frequency. The trip current decreases as the duty cycle increases. There is a minimum compensation slope that will guarantee that the system is unconditionally stable. The inequality below describes this relationship:

$$S_{COMPENSATION} \ge S_{CHARGE} (2 DC - 1)/(1 - DC)$$

(2-4)

$S_{COMPENSATION}$  is the slope of the compensation voltage and  $S_{CHARGE}$  is the slope of the inductor charging waveform. Fortunately, most modern current mode ICs provide internal slope compensation that can be used "as is" or modified if necessary. For older parts, such as the 1846A, either a manufacturer's application note or the data sheet will give the information necessary to calculate the appropriate amount of slope compensation. TI Application Note U-97 and Linear Technology Application Note 19 give detailed analyses of slope compensation.

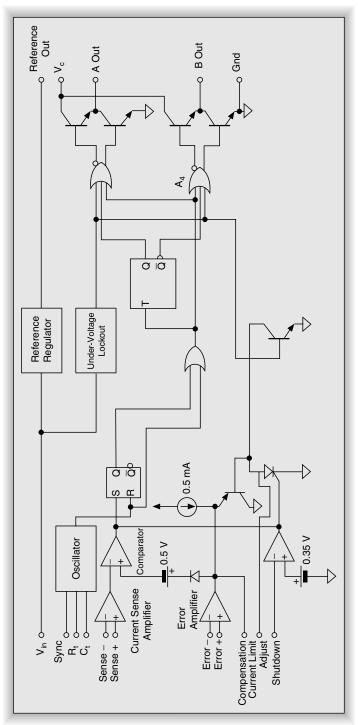

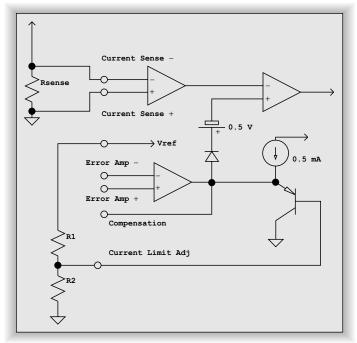

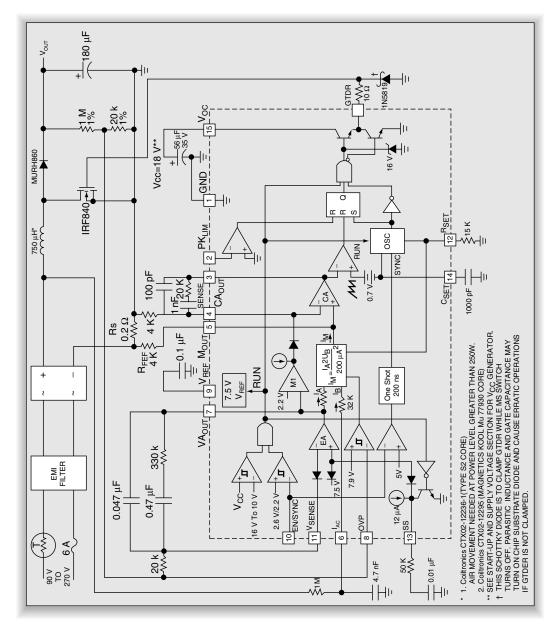

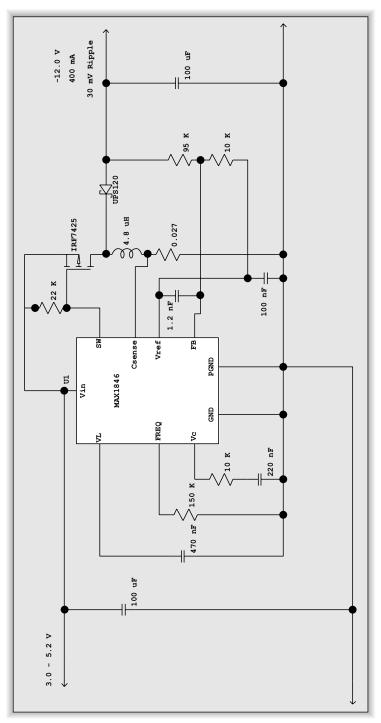

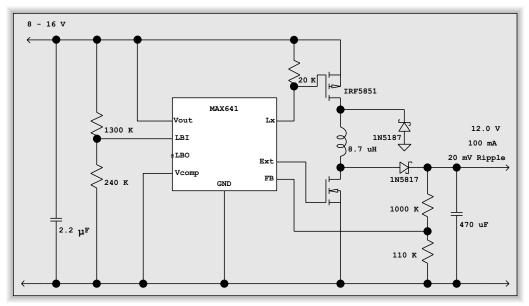

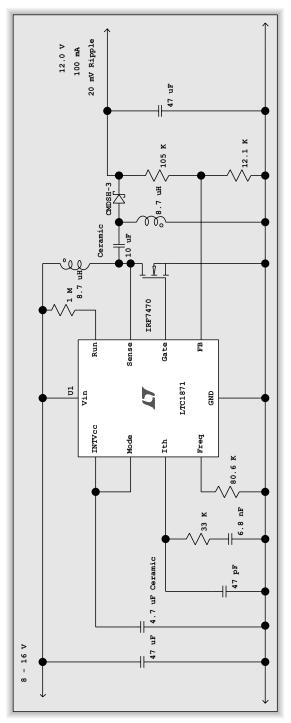

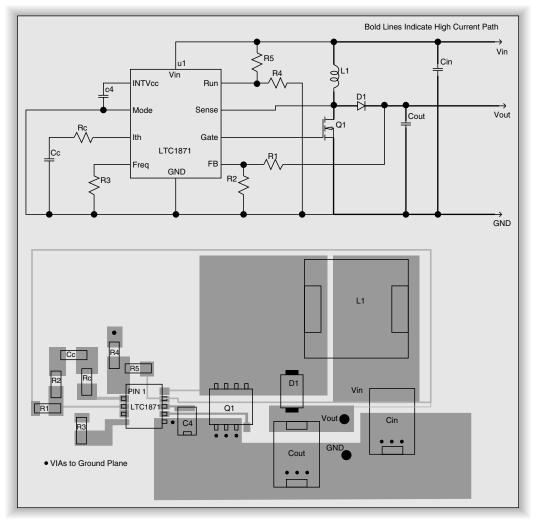

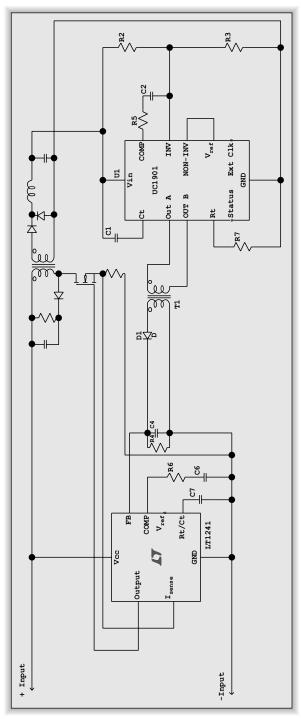

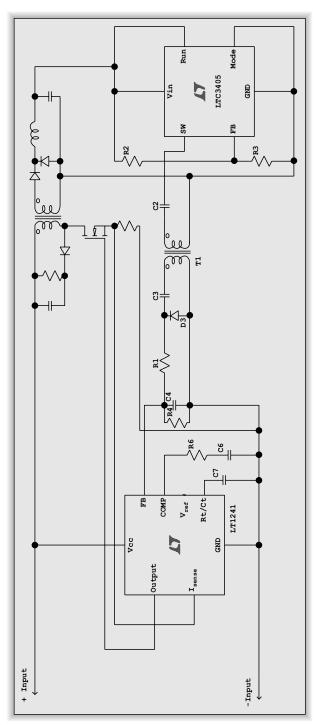

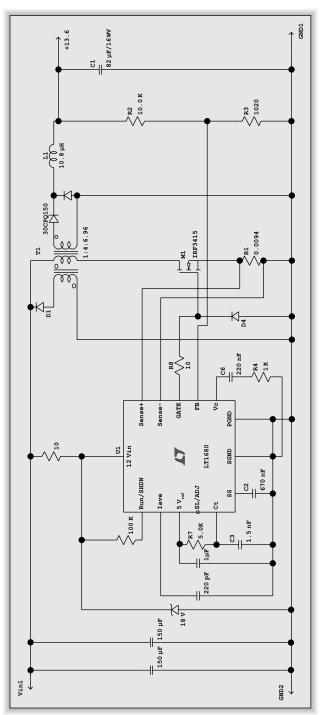

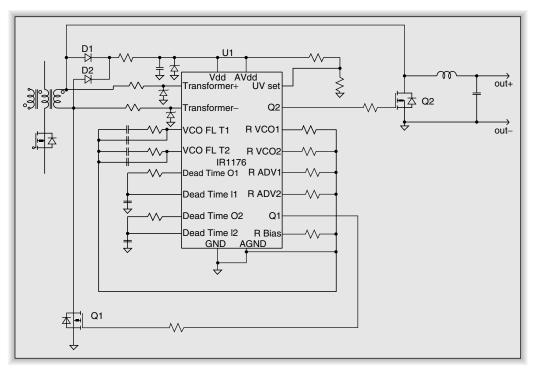

### A Representative Current Mode PWM Controller

The 1846A is representative of a third-generation controller. Figure 2-15 illustrates the internal circuitry of the 1846A. The oscillator and reference are basically the same circuit as used in the 1526A. The 1846A oscillator can be synchronized to another 1846A or to an external oscillator in the same way as performed on the 1526A. The under-voltage lockout circuit is different in that it uses the input voltage to make the lockout decision rather than the reference voltage. The under-voltage lockout holds the device in reset as long as the input voltage is below 8.0 V. The lockout circuit has 0.75 V of hysteresis to ensure that noise or slowly rising input voltage will not cause an unstable condition at turn on.

The error amplifier is a transconductance amplifier with an "open collector" output similar to that in the 1526A.

The current sense amplifier is a voltage difference amplifier with a gain of three. The diode and voltage source in series with the inverting input of the

Figure 2-15: Internal circuitry of the 1846A PWM controller

PWM comparator limit the voltage to about 3.5 V (4.6 V error signal max. minus 0.5 V minus one diode drop). This means that a current sense amplifier output above 3.5 V will not shut off the output pulse. This constrains the current sense voltage to be less than 1.1 V because of the gain of three in the current sense amplifier.

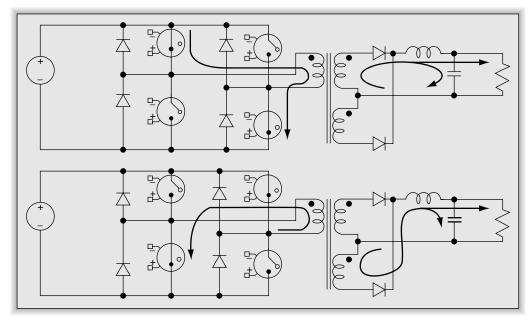

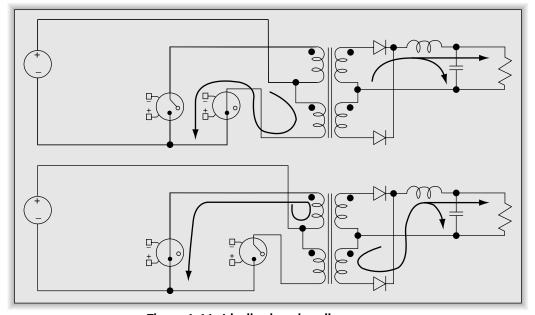

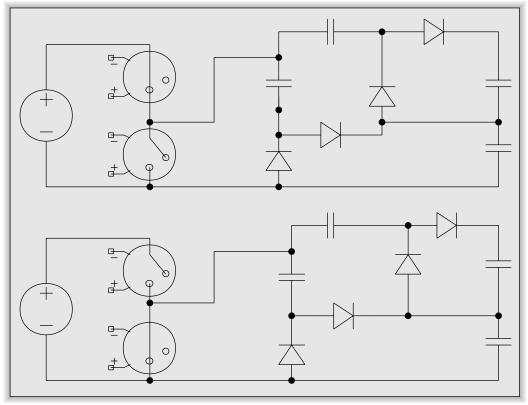

The inverting and noninverting inputs have a common mode range of ground to  $V_{IN}$  – 3 V. This allows the current sense amplifier to be used in boost, buck, forward, and flyback designs. Figure 2-16 shows three different methods of implementing current sense. The resistor and capacitor in Figure 2-16(a) are usually necessary to reduce the size of turn-on transients in the switch. In both bipolar and FET switches, there is coupling between the high voltage side of the switch (collector/drain) and the current sense resistor. The transient that couples to the current sense resistor can cause a false termination of the output pulse. The resistor and capacitor limit the rise time and reduce the transient so proper operation occurs. Buck designs will require that the input voltage is at least 3 V above the output voltage if a current sense resistor is used. In circuits where there is not sufficient common mode range or when total isolation is required (as in bridge circuits), the current limit amplifier can be driven by an isolating current transformer. A current transformer is also advantageous in very-high-current applications because it can reduce the voltage and, therefore, the power consumed by the current sense. The diode in figure 2-16(c) is necessary so that the voltage at the noninverting amplifier input does not go more than one diode drop negative from ground.

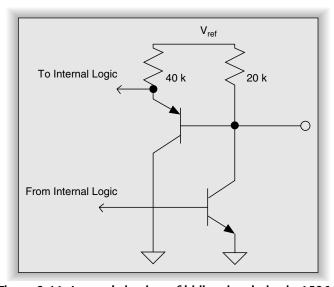

The shutdown circuit, the under-voltage lockout circuit, and the current limit circuit clamp the output voltage of the error amplifier. The current limit pin is

Figure 2-16: Three different methods of implementing current sensing: (a) grounded resistor; (b) floating resistor; and (c) with an isolating current transformer

used to limit the maximum inductor current by clamping the error amplifier output below the 4.6 V maximum of the error amplifier. The error amplifier output is clamped to a voltage equal to one diode drop (the base-emitter voltage) of the current limit set transistor. Figure 2-17 shows a typical connection to the current limit pin. The current limit is not directly set by the voltage at the current limit pin, but, rather, it sets the current sense output voltage that will terminate a pulse. Since the diode drop in series with the inverting comparator input is roughly equal to the base-emitter voltage, the trip point is equal to the current limit voltage minus the 0.5 V offset. The equations below allow you to set the current limit:

$$V_{\text{CURRENT LIMIT}} = R_1/(R_1 + R_2) * V_{\text{REF}}$$

(2-5)

$$V_{\text{CURRENT SENSE}} = (V_{\text{CURRENT LIMIT}} - 0.5)/3$$

(2-6)

$$I_{CURRENT LIMIT} = V_{CURRENT SENSE} / R_{SENSE}$$

(2-7)

$R_2$  has a secondary function of supplying the holding current for the shutdown latch. If you desire the shutdown to latch,  $R_2$  must be below 2.5 k $\Omega$  to supply at least 1.5 mA of current to hold the latch. When the shutdown signal goes below 350 mV, the shutdown circuit will shut off the PWM latch and hold the IC in reset until a power cycle occurs. Selecting  $R_2$  greater than 5 k $\Omega$  will allow the shutdown circuit to reset the PWM latch and discharge any capacitance on the current limit set pin, but when the shutdown signal is removed, a new start sequence will begin.

This IC does not provide soft start circuitry. Soft start is accomplished by adding a capacitor to ground on the current limit pin. The current limit pin sets the peak current trip point, so raising the voltage slowly on the current sense pin will provide the soft start function.

You will notice that it is possible for the comparator to fail to set the flip-flop before a new oscillator cycle occurs if the inductor current is quite low and the error signal commands a large inductor current. This would cause the duty cycle to be greater than 100%. The signal presented to the output logic is the OR of the oscillator pulse and the flip-flop output. The short pulse from the oscillator will guarantee a short dead time on the output equal to the discharge time of the timing capacitor. You can adjust the length of the dead time by

Figure 2-17: 1846 current limit pin implementation

changes to the relative values of the timing resistor and capacitor. The data sheet gives a nomograph for setting the dead time.

The output logic and totem-pole outputs of the 1846A are similar to that of the 1526A. You must follow the same precautions of limiting the current into the collector supply during the crossover in the output transistors. You must similarly limit the output current when driving FET switches by using series resistors.

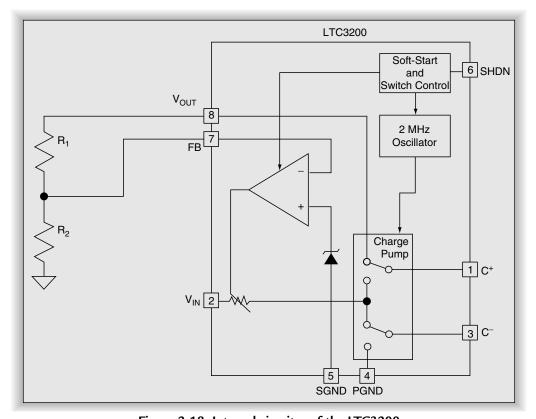

## Charge Pump Circuits

IC manufacturers continue to improve the output capability of charge pump converters. Switch frequency and switch on resistance are the two parameters which affect power dissipation and indirectly affect efficiency and maximum output current. Charge pump circuits have an equivalent series resistance that is given by:

$$R_{EO} = 1/F_{SWITCH}C_{FLYING}$$

(2-8)

This equivalent resistance is a property of the switched capacitor circuit and is not an actual physical resistance. You can see that we can improve performance (lowering  $R_{EQ}$ ) by raising the frequency or increasing the flying capacitor. Performance is only increased until the internal physical resistance of the switches approaches the equivalent resistance of the switching circuit. In general, charge pump ICs can be used in parallel to achieve greater output current.

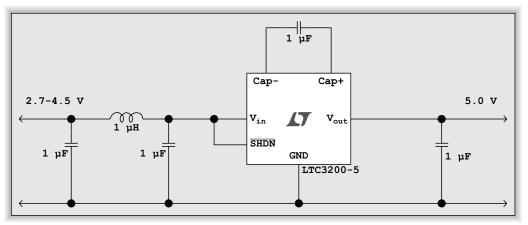

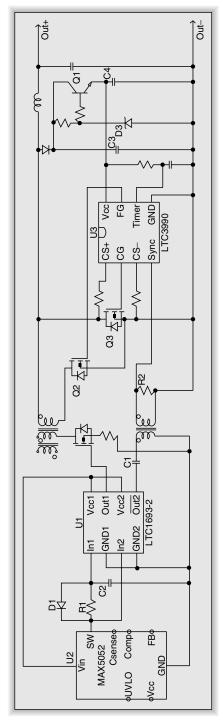

Figure 2-18 shows the internal circuit of the LTC3200, which is a representative voltage doubling charge pump that provides a regulated output. The circuit contains a 2-MHz fixed-frequency oscillator that drives the switch circuit with a two-phase nonoverlapping clock. The error amplifier compares the voltage at the feedback pin to the internal 1.268-V zener voltage reference. The output of the error amplifier controls the amount of current that can flow into the flying capacitor during phase one of the clock. Phase two of the clock connects the

Figure 2-18: Internal circuitry of the LTC3200

flying capacitor in series with the input voltage to provide current to the load and output capacitor.

This charge pump controller has a soft start and switch control circuit to limit the current draw from the input supply. The switch control circuit shuts down the system if the IC gets hotter than 160°C and reenables the circuit around 150°C. This circuit also limits output current to 225 mA in the case of a short circuit.

The LTC3200 will produce a regulated output between 1.268 V and 5.5 V, up to 100 mA. The input voltage range is 2.7 V to 4.5 V. This can accommodate a single lithium cell, three alkaline cells, three NiCad cells, or three NiMH cells. The current control circuit allows the IC to regulate the output to a voltage above or below the input voltage. Efficiency suffers for output below the input, however. The output voltage is set with a voltage divider between the output pin and the feedback pin. The equation for the output voltage is:

$$V_{OUT} = 1.268 (1 + (R_1/R_2))$$

(2-9)

The resistors can range from several kilohms to 1 M $\Omega$ . If the output voltage will be below the input voltage, it is necessary to put a 1 mA load on the output to ensure that the voltage does not creep up at very light loads.

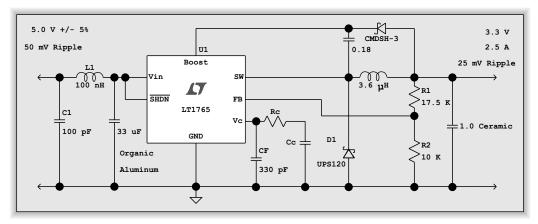

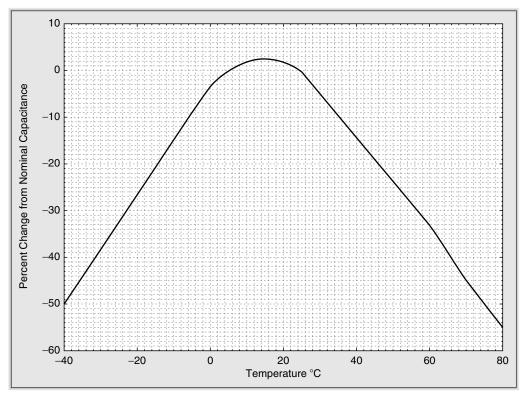

The input capacitor, output capacitor, and flying capacitor are all required to have low ESR. These capacitors need to be greater than 0.5  $\mu$ F, but values up to only 1  $\mu$ F will be adequate for good output current and low ripple. Electrolytic and tantalum capacitors will not have low enough ESR to work properly. Ceramic capacitors are the preferred type. Ceramic capacitors have a significant temperature coefficient depending on the type of dielectric. X5R and X7R capacitors have the smallest change in value over temperature. Another consideration is the change in capacitance with applied voltage. Z5U and Y5V capacitors have significant changes in capacitance with applied voltage. The output capacitor ESR must be below 0.3  $\Omega$  in order for the error amplifier to remain stable. If the ESR is higher, the amplifier response is no longer a single pole rolloff and can become unstable.

The LTC3200 uses a variable resistance to modulate the charge current, so there is some amount of power dissipated in the IC in order to maintain a regulated

output. The LT1516 is an example of a charge pump that uses burst mode to maintain a regulated 5.0 V output. This circuit trades off higher ripple voltage (100 mV at full load) and a second-order filter problem for increased efficiency.

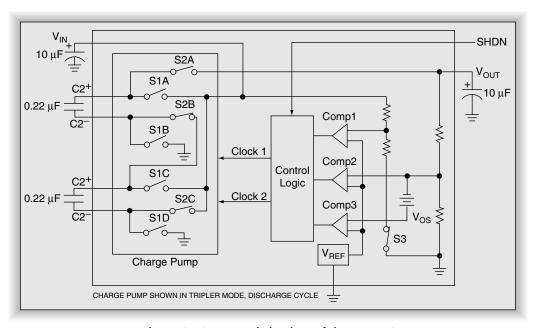

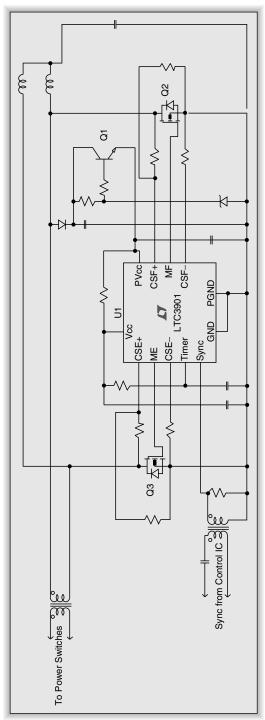

Figure 2-19 shows the internal circuit of the LT1516. Comparator 2 compares the divided output voltage against the internal reference. If the voltage is below the threshold, the charge pump switches are enabled and charge is transferred from the input to the output until the output rises above the upper comparator 2 trip point. This burst mode causes a low-frequency ripple in the output equal to the hysteresis in comparator 2. There is also high-frequency ripple in the output due to the switching of the charge pump while charging the output capacitor.

The LT1516 uses two flying capacitors to implement either a voltage tripling or voltage doubling configuration. Whenever  $V_{\rm IN}$  is less than 2.55 V, comparator 1 forces the control logic to put the device in voltage tripler mode. During the charge phase, the switches place both flying capacitors from input to ground. During the discharge phase, the flying capacitor C1 is placed in series with C2 and the series combination is placed in series with the input. Once  $V_{\rm IN}$  is

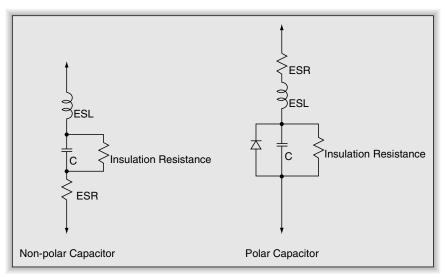

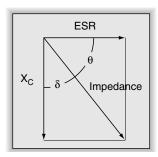

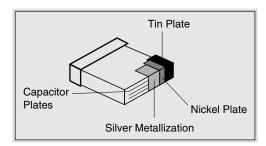

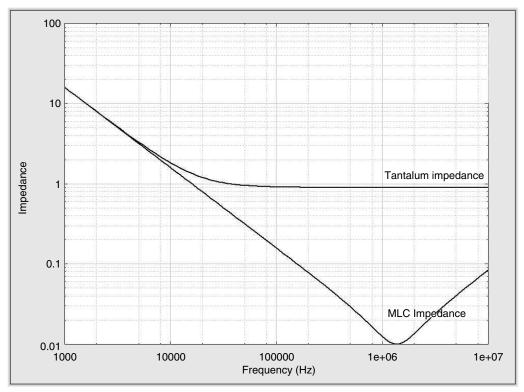

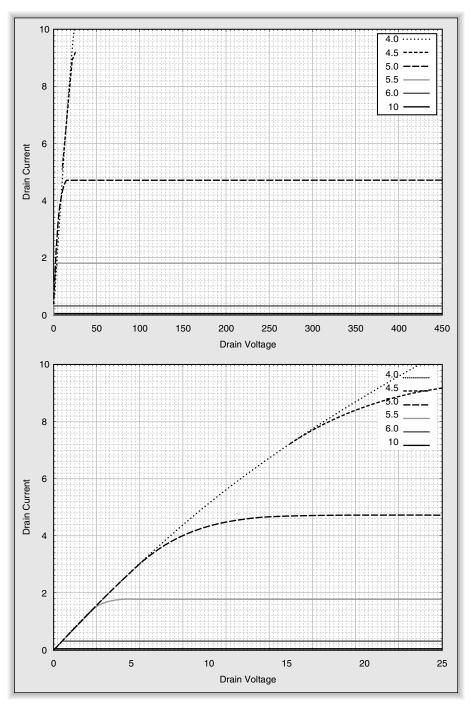

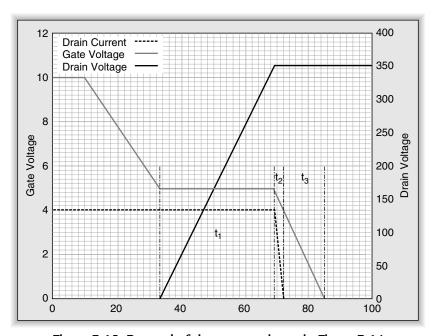

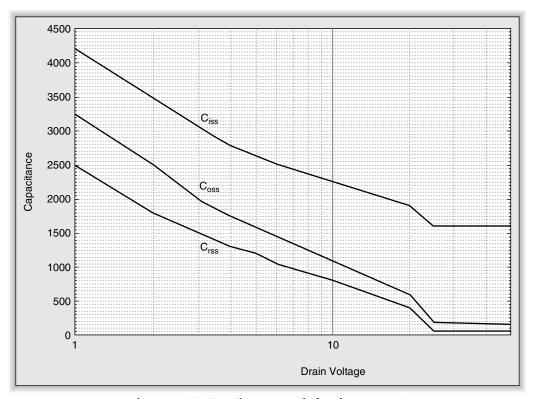

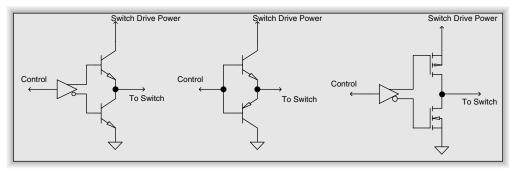

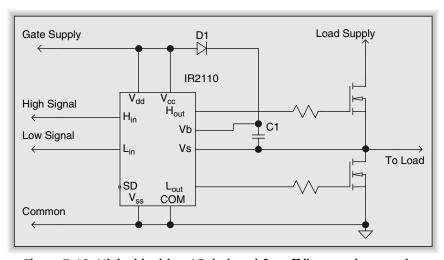

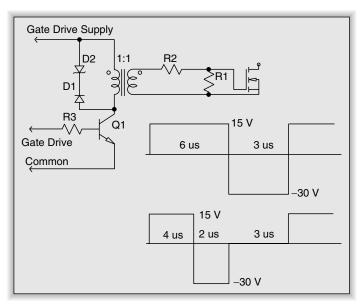

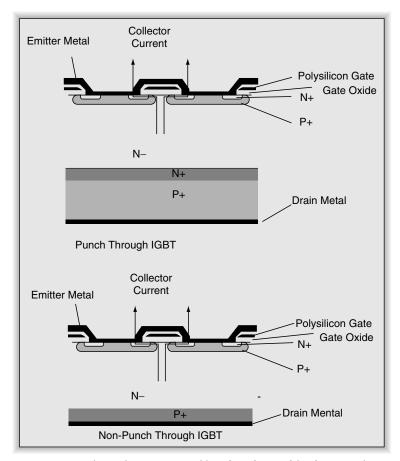

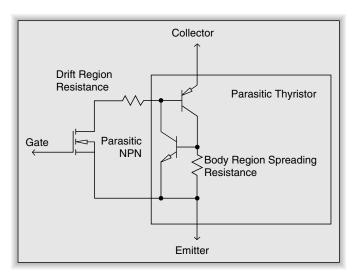

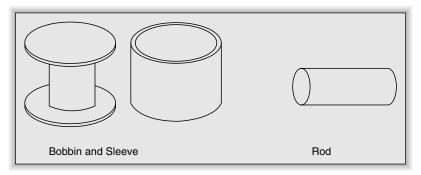

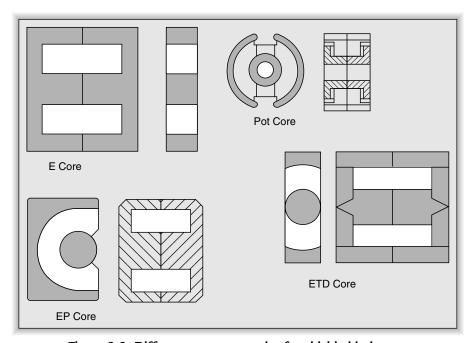

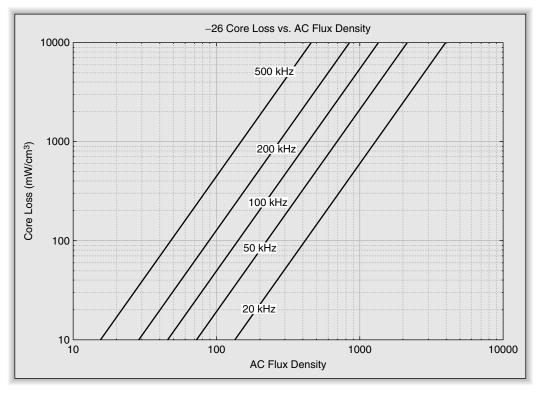

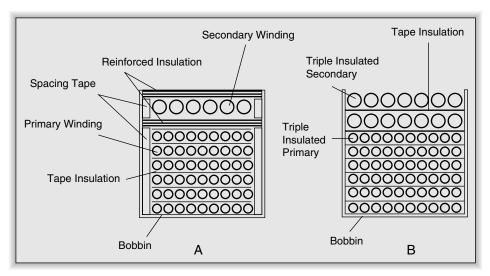

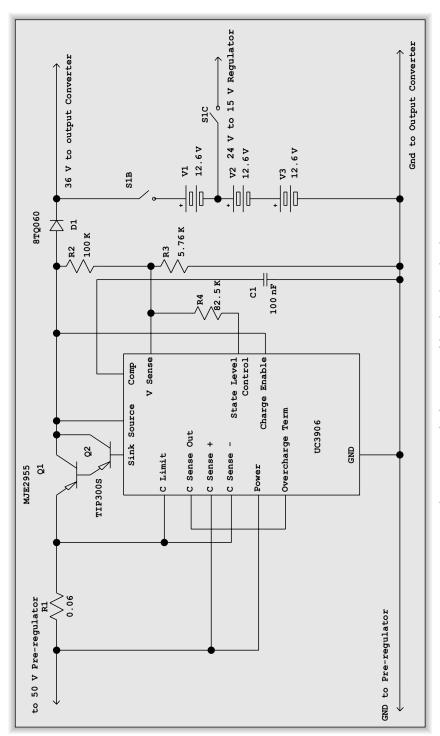

Figure 2-19: Internal circuitry of the LT1516